搜索到

5

篇与

的结果

-

-

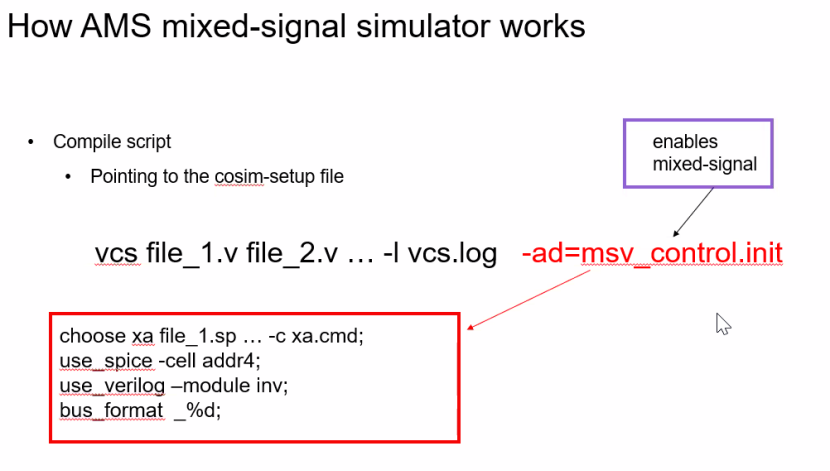

vcs debug rtl或者netlist 中的loop 当仿真出现如下的提示,说明遇到了 loop,可以在 vcs compile option 中用+vcs+loopreport 来报 loop 的点,但耗时较长并且报出来的位置不精准,遇到这种情况,可以用下面这种方法来快速定位 loop 的位置创建 loop_detect.tcl,放在仿真目录。脚本内容如下:2.增加 compile option:-debug_all3.正常执行仿真,当出现 loop 信息时 ctrl+c 暂停后执行source loop_detect.tcl执行 loop_detect 1000(1000 可以修改,num 越大,打印的信息越多)执行完成后在仿真目录下会生成一个 loop.txt 文件这里发现是在 pad 中发生了 loop,将 pad 的 IE force 成 0 继续往下跑,loop 被打断,因为 force 的原因会出现 mismatch,当 mismatch 数量超过 10 个会退出仿真,为了让仿真跑完可以把 tb 里的_miscompare_limit 限制改大一点,让它继续往下跑。每次出现 loop 都完成上述 1-5 的操作,直到所有的 loop 打断(miamatch 不用管)。将所有的 loop 点记录下来后,去 flow 中做 eco,重新跑 atpg,再仿真,就全部 pass了。最终 eco 的 loop 点有

vcs debug rtl或者netlist 中的loop 当仿真出现如下的提示,说明遇到了 loop,可以在 vcs compile option 中用+vcs+loopreport 来报 loop 的点,但耗时较长并且报出来的位置不精准,遇到这种情况,可以用下面这种方法来快速定位 loop 的位置创建 loop_detect.tcl,放在仿真目录。脚本内容如下:2.增加 compile option:-debug_all3.正常执行仿真,当出现 loop 信息时 ctrl+c 暂停后执行source loop_detect.tcl执行 loop_detect 1000(1000 可以修改,num 越大,打印的信息越多)执行完成后在仿真目录下会生成一个 loop.txt 文件这里发现是在 pad 中发生了 loop,将 pad 的 IE force 成 0 继续往下跑,loop 被打断,因为 force 的原因会出现 mismatch,当 mismatch 数量超过 10 个会退出仿真,为了让仿真跑完可以把 tb 里的_miscompare_limit 限制改大一点,让它继续往下跑。每次出现 loop 都完成上述 1-5 的操作,直到所有的 loop 打断(miamatch 不用管)。将所有的 loop 点记录下来后,去 flow 中做 eco,重新跑 atpg,再仿真,就全部 pass了。最终 eco 的 loop 点有 -

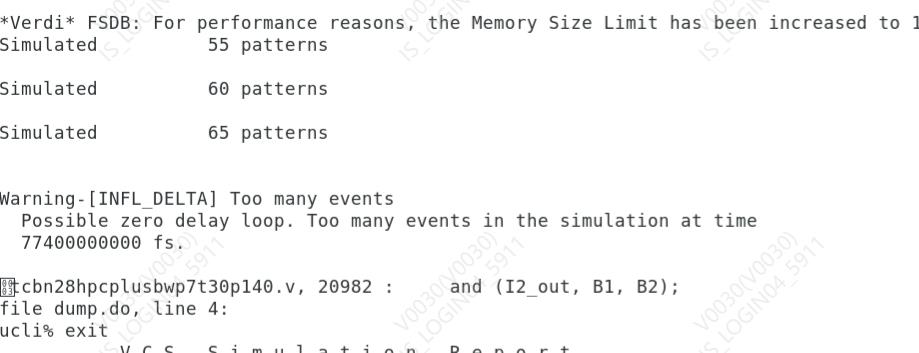

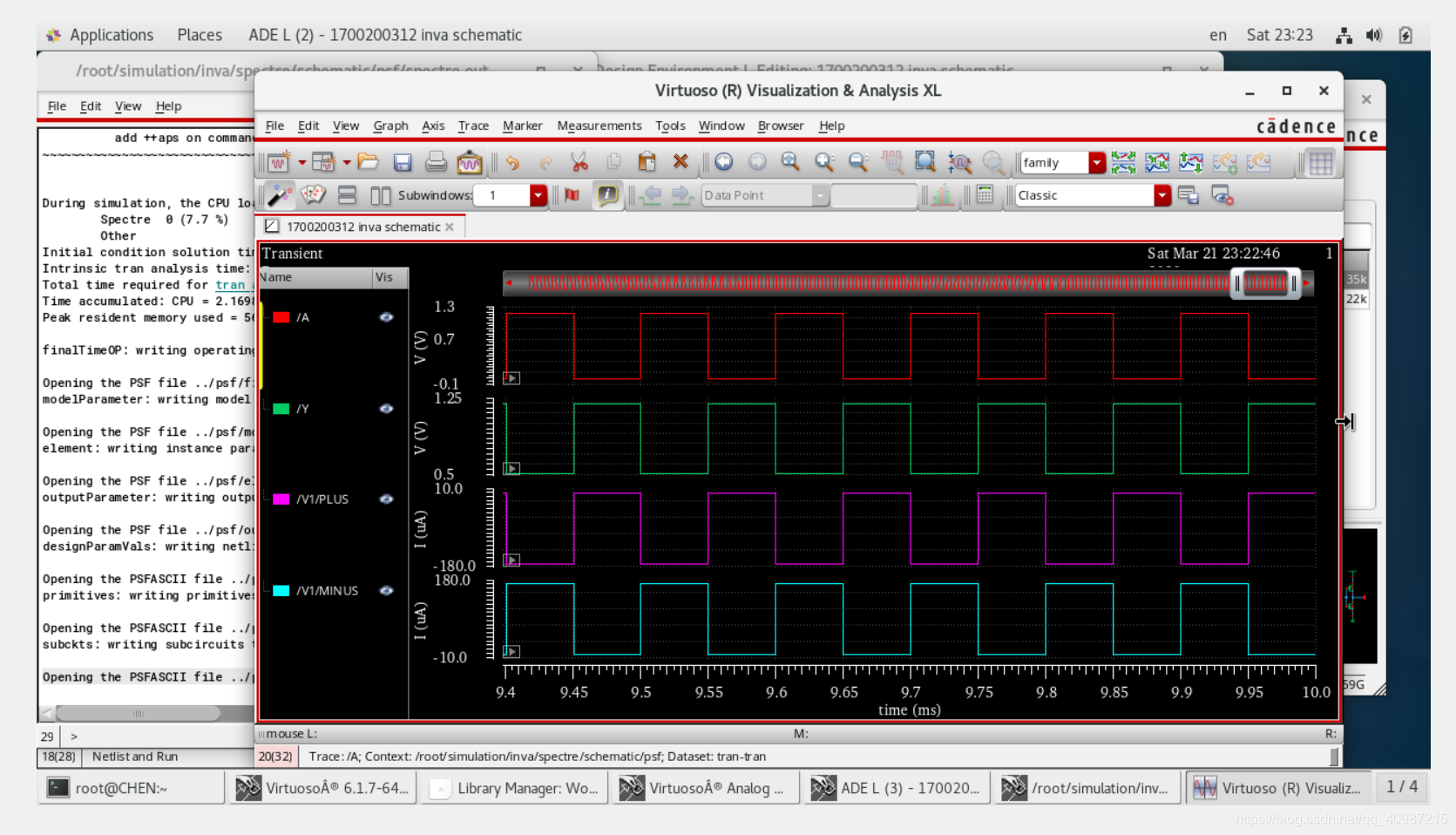

在IC617中进行xa+vcs数模混仿 基本介绍:本文档介绍了在IC617的ADE L环境的图形化界面中进行数字+模拟信号混合仿真的方法,主要分成以下几个部分:一、软件要求1、与CustomSim兼容的VCS,本文档中分别是xa2018.09和vcsmx_v2018092、Custom Waveview(波形查看软件,非必须)3、IC614或更新版本的Cadence(OA)或更新版本的IC5.1.4.1-USR5(CDBA),本文档以IC617为例。4、相应的license二、安装并设置CustomSim ADE L交互界面安装CustomSim有两种方式,分别是安装在Cadence目录中和目录外。本文档只介绍第二种方法,即安装在Cadence目录外。具体步骤如下:1、设置环境变量:setenv CDS_LOAD_ENV CSF2、在CustomSim的安装目录下找到名为CustomSim.cdsenv的文件,位置在CustomSim安装目录/ade/CustomSimADE/CustomSim.cdsenv,将其复制到home目录下。(这是CustomSim的初始化文件,不复制也无所谓)3、在home下找到.cdsinit文件并在文件中将CustomSim.ile文件的路径添加进去:Load(“CustomSim安装目录/ade/CustomSimADE/CustomSim.ile”)(这里面包含了Cadence环境下的CustomSim ADE SKILL代码)4、设置环境变量:setenv CDS_Netlisting_Mode Analog5、如果Cadence版本早于IC617且CustomSimADE版本晚于M-2017.03,则需要设置如下环境变量:setenv CDS_AUTO_64BIT ALL(在本文档中不需要进行此设置,但设置了也无妨。)6、全部设置完成后就可以按照正常的方式启动Cadence软件了。三、CustomSim ADE L的使用CustomSim ADE交互界面支持Cadence的schematic和config两种方式的设置。Schematic通常用于纯模拟仿真(CustomSim)而config通常用于混合信号仿真(CustomSim-VCS),本文档使用第二种方法。下面是设置数模混合仿真的具体步骤:1、创建原理图:新建schematic并将具体的原理图电路添加进去,模拟部分按照正常的方式创建电路并生成symbol,数字电路的创建方法有如下几种:①新建cell view,类型选择Verilog,view会自动变成functional,确定之后在里面编辑数字电路,保存并检查无误后会自动弹出生成symbol的界面,完成之后就可以用平时调用模拟电路的方法调用该模块。②大多数情况下模拟工程师并不需要写数字代码,只需要将写好的代码调用即可,此时可以用之前的方式新建verilog之后将数字代码复制进来即可。(也可以找到代码的路径将数字代码复制过去覆盖原来的代码,并修改好数字里面的module名字,重新打开该verilog再保存退出,同样可以弹出生成symbol的界面。)③CustomSim也提供了直接加载数字代码的方式,本文档不做介绍。2、创建config:创建config的名字需要和schematic相同,类型选择config,完成后会弹出一个名为New Configuration的窗口,点击view那一栏并选择schematic(唯一的选项),然后Global Bindings需要进行设置,设置之前先对各个选项做简要介绍:①Library List:Library列表,可以是Cadence自带的library,可以是工艺库,也可以是用户自定义的库,可以定义一个,也可以定义多个,如果定义多个需要用空格隔开。②View List:即之前定义过的库中所包含的view都会在里面显示。CustomSim支持的View List包括:hspiceD、spice、cmos_sch、veriloga和schematic。③Stop List:此处的内容定义了生成网表的类型,如果想生成spectre格式的网表需要在此栏填写spectre同时View List栏也需要加入spectre,如果想生成HSPICE格式的网表则需要在两栏同时填写hspiceD或者HSPICE。(注意此栏不要填错,要根据你使用的仿真器类型填写。④Constraint List:(作用不明)实际设置:可以直接点击底部的Use Template然后选择AMS并确定,实测可以成功仿真而无需额外设置,前提是使用spectre仿真。点击ok完成设置会弹出新的界面,在界面中找到ADE L选项并点击就会启动ADE界面和schematic界面。接下来的就可以关闭config界面进行下一步的设置了。四、电路设置这一步的设置方法基本与平时相同,也比较简单。1、点击Setup→Simulator/Directory/Host在弹出的界面选择CustomSim作为仿真器并确认(仿真路径可以按照自己的需求设置,不设置也可)。2、如果你之前的原理图中已经同时包含了数字和模拟模块,CustomSim就会自动选择仿真类型为混合信号仿真,无需手动设置。五、ADE环境下CustomSim的设置这一步主要是对仿真器的部分重要选项进行设置,主要是仿真器的选择和网表类型的选择。具体如下:1、在ADE L界面点击Setup→Environment会弹出设置界面:在其中可以看到Simulator Selection/Netlist Syntax/Waveform Output Format等选项。此处我们选择:CunstomSim/spectre/fsdb+fsdb(分别对应仿真器/网表/数字波形格式+模拟波形格式,波形格式可以根据自己的喜好和使用的看波形的软件设置),另外# of Cores是多核仿真选项,默认为1,如果需要加快仿真速度可以在其中填入需要的CPU的数量,如需要8颗CPU则在里面填写8(需要注意的是CPU数量并非会全部用到,仿真器会自己决定用到的数目,例如填了8,实际可能只用到了6,但不会超过8,猜测跟实际的电路复杂程度有关。)2、仿真选项设置:点击Simulation→Option→Digital,在top name栏点击Use Top Cell Name,并确定。(这一步很重要,不进行此设置仿真会无法继续)3、设置transient仿真:点击Analyses→Choose后在stop栏填入需要的仿真时间并确定。(只有tran可选)4、另外还有Model的添加,以及其它的自定义的设置再次不过多介绍。可以自行试验。六、波形保存上一步结束后就已经可以进行仿真了,但为了加快仿真速度,通常会减少保存的波形节点的数量,这一步介绍保存的方法。点击Optput→To Be Saved→Select On Design之后再原理图中依次选择需要保存的节点电压和电流,按esc完成选择。七、开始仿真Simulation→Netlist and Run开始仿真!八、常见错误及解决方法上一步中可能会有如下错误:如果模拟电路中调用了电阻且电阻是多跟串联的形式,仿真器可能会报错并提示存在器件名字和net冲突的问题,此时只需要将其中一个的名字改掉就可以了。具体方法不做赘述。九、参考文档CustomSim User Guide的CustomSim ADE Interface Integration部分。ps:仅做记录学习用,个人不推荐,仿真还是要使用自动化的命令效率才高,debug 才需要图形界面。

在IC617中进行xa+vcs数模混仿 基本介绍:本文档介绍了在IC617的ADE L环境的图形化界面中进行数字+模拟信号混合仿真的方法,主要分成以下几个部分:一、软件要求1、与CustomSim兼容的VCS,本文档中分别是xa2018.09和vcsmx_v2018092、Custom Waveview(波形查看软件,非必须)3、IC614或更新版本的Cadence(OA)或更新版本的IC5.1.4.1-USR5(CDBA),本文档以IC617为例。4、相应的license二、安装并设置CustomSim ADE L交互界面安装CustomSim有两种方式,分别是安装在Cadence目录中和目录外。本文档只介绍第二种方法,即安装在Cadence目录外。具体步骤如下:1、设置环境变量:setenv CDS_LOAD_ENV CSF2、在CustomSim的安装目录下找到名为CustomSim.cdsenv的文件,位置在CustomSim安装目录/ade/CustomSimADE/CustomSim.cdsenv,将其复制到home目录下。(这是CustomSim的初始化文件,不复制也无所谓)3、在home下找到.cdsinit文件并在文件中将CustomSim.ile文件的路径添加进去:Load(“CustomSim安装目录/ade/CustomSimADE/CustomSim.ile”)(这里面包含了Cadence环境下的CustomSim ADE SKILL代码)4、设置环境变量:setenv CDS_Netlisting_Mode Analog5、如果Cadence版本早于IC617且CustomSimADE版本晚于M-2017.03,则需要设置如下环境变量:setenv CDS_AUTO_64BIT ALL(在本文档中不需要进行此设置,但设置了也无妨。)6、全部设置完成后就可以按照正常的方式启动Cadence软件了。三、CustomSim ADE L的使用CustomSim ADE交互界面支持Cadence的schematic和config两种方式的设置。Schematic通常用于纯模拟仿真(CustomSim)而config通常用于混合信号仿真(CustomSim-VCS),本文档使用第二种方法。下面是设置数模混合仿真的具体步骤:1、创建原理图:新建schematic并将具体的原理图电路添加进去,模拟部分按照正常的方式创建电路并生成symbol,数字电路的创建方法有如下几种:①新建cell view,类型选择Verilog,view会自动变成functional,确定之后在里面编辑数字电路,保存并检查无误后会自动弹出生成symbol的界面,完成之后就可以用平时调用模拟电路的方法调用该模块。②大多数情况下模拟工程师并不需要写数字代码,只需要将写好的代码调用即可,此时可以用之前的方式新建verilog之后将数字代码复制进来即可。(也可以找到代码的路径将数字代码复制过去覆盖原来的代码,并修改好数字里面的module名字,重新打开该verilog再保存退出,同样可以弹出生成symbol的界面。)③CustomSim也提供了直接加载数字代码的方式,本文档不做介绍。2、创建config:创建config的名字需要和schematic相同,类型选择config,完成后会弹出一个名为New Configuration的窗口,点击view那一栏并选择schematic(唯一的选项),然后Global Bindings需要进行设置,设置之前先对各个选项做简要介绍:①Library List:Library列表,可以是Cadence自带的library,可以是工艺库,也可以是用户自定义的库,可以定义一个,也可以定义多个,如果定义多个需要用空格隔开。②View List:即之前定义过的库中所包含的view都会在里面显示。CustomSim支持的View List包括:hspiceD、spice、cmos_sch、veriloga和schematic。③Stop List:此处的内容定义了生成网表的类型,如果想生成spectre格式的网表需要在此栏填写spectre同时View List栏也需要加入spectre,如果想生成HSPICE格式的网表则需要在两栏同时填写hspiceD或者HSPICE。(注意此栏不要填错,要根据你使用的仿真器类型填写。④Constraint List:(作用不明)实际设置:可以直接点击底部的Use Template然后选择AMS并确定,实测可以成功仿真而无需额外设置,前提是使用spectre仿真。点击ok完成设置会弹出新的界面,在界面中找到ADE L选项并点击就会启动ADE界面和schematic界面。接下来的就可以关闭config界面进行下一步的设置了。四、电路设置这一步的设置方法基本与平时相同,也比较简单。1、点击Setup→Simulator/Directory/Host在弹出的界面选择CustomSim作为仿真器并确认(仿真路径可以按照自己的需求设置,不设置也可)。2、如果你之前的原理图中已经同时包含了数字和模拟模块,CustomSim就会自动选择仿真类型为混合信号仿真,无需手动设置。五、ADE环境下CustomSim的设置这一步主要是对仿真器的部分重要选项进行设置,主要是仿真器的选择和网表类型的选择。具体如下:1、在ADE L界面点击Setup→Environment会弹出设置界面:在其中可以看到Simulator Selection/Netlist Syntax/Waveform Output Format等选项。此处我们选择:CunstomSim/spectre/fsdb+fsdb(分别对应仿真器/网表/数字波形格式+模拟波形格式,波形格式可以根据自己的喜好和使用的看波形的软件设置),另外# of Cores是多核仿真选项,默认为1,如果需要加快仿真速度可以在其中填入需要的CPU的数量,如需要8颗CPU则在里面填写8(需要注意的是CPU数量并非会全部用到,仿真器会自己决定用到的数目,例如填了8,实际可能只用到了6,但不会超过8,猜测跟实际的电路复杂程度有关。)2、仿真选项设置:点击Simulation→Option→Digital,在top name栏点击Use Top Cell Name,并确定。(这一步很重要,不进行此设置仿真会无法继续)3、设置transient仿真:点击Analyses→Choose后在stop栏填入需要的仿真时间并确定。(只有tran可选)4、另外还有Model的添加,以及其它的自定义的设置再次不过多介绍。可以自行试验。六、波形保存上一步结束后就已经可以进行仿真了,但为了加快仿真速度,通常会减少保存的波形节点的数量,这一步介绍保存的方法。点击Optput→To Be Saved→Select On Design之后再原理图中依次选择需要保存的节点电压和电流,按esc完成选择。七、开始仿真Simulation→Netlist and Run开始仿真!八、常见错误及解决方法上一步中可能会有如下错误:如果模拟电路中调用了电阻且电阻是多跟串联的形式,仿真器可能会报错并提示存在器件名字和net冲突的问题,此时只需要将其中一个的名字改掉就可以了。具体方法不做赘述。九、参考文档CustomSim User Guide的CustomSim ADE Interface Integration部分。ps:仅做记录学习用,个人不推荐,仿真还是要使用自动化的命令效率才高,debug 才需要图形界面。 -

EDA-IC设计平台 Synopsys tools套装 VCS2018 Verdi2018 链接: https://pan.baidu.com/s/1pcuTqFEkMmgndafvnhlzlA 提取码: cm7e 复制这段内容后打开百度网盘手机App,操作更方便哦 --来自百度网盘超级会员v3的分享安装好的EDA环境,解压可以直接使用:环境为vmware虚拟机;解压后,使用vmware打开启动,选择“我已移动”,有问题可以联系我。链接: https://pan.baidu.com/s/1lvp4WUzRCQIZmHM8wrHSyw 提取码: 8q4c 复制这段内容后打开百度网盘手机App,操作更方便哦 --来自百度网盘超级会员v3的分享账户root密码:2020License到2030年安装1)安装installer提示:教程非本人所写,稍有改动,原文详见图片logo进入到synopsysinstaller_v5.0目录下,先运行.run文件,然后提示你输入安装路径,默认回车在当下目录就行;完成后直接运行生成的setup.sh文件。但是会出现如下error。sudo ./SynopsysInstaller_v5.0.run./setup.sh这个问题应该是缺少依赖库,先查找这个库出自那个安装包,然后进行安装。安装过程中会有提示,输入“y”回车就行。repoquery --nvr --whatprovides libXss.so.1sudo yum install libXScrnSaver-1.2.2-6.1.el7依赖库安装好后,再次运行 “./setup.sh”就会出现安装界面了。2)安装IC软件进入到home目录下,新建synopsys的文件夹,以后synopsys的软件均安装在这个目录下;home不是在普通用户下,需要超级用户权限,而软件安装必须在普通用户下所以需要将这个文件加权限打开;sudo mkdir synopsyssudo chmod 777 synopsys然后回到install目录下,运行“./setup.sh”开始安装,点击start;默认,点击next。这里需要选择安装包的路径,我们先安装scl,选择好点击ok;这里选择我们安装路径,选择我们上面新建的synopsys目录下。全部选上,next。安装确认,没有问题点击next;点击接受并安装,安装完成点击 Finish,然后点击Dismiss完成;其他synopsys软件也是这样步骤,依次安装完就行!4.license生成、环境以及激活1)启动scl_keygen生成器这个需要在window下进行,双击运行scl_keygen.exe.需要填写这4项信息,HOST ID Daemon 和HOST ID Feature填写一样的,Port选择27000。进入虚拟机,打开terminal使用以下命令查找hostnameifconfig我的填写如下,然后点击Generate生成license打开生成licens文件,修改第二行,这个需要与虚拟机里面scl路径一致,不然license无效。修改好后把这个文件复制到共享文件中。这个文件最后需要放到这个“scl/2018.06/admin/license/”目录下,要与环境里面设置的路径一致。2)环境设置打开.bashrc环境文件,加入以下内容,对应自己安装路径。但是需要注意倒数第二行,需要确认主机名是否正确。保存退出,source一下。export DVE_HOME=/home/synopsys/vcs/O-2018.09-SP2 export VCS_HOME=/home/synopsys/vcs/O-2018.09-SP2 export VCS_MX_HOME=/home/synopsys/vcs-mx/O-2018.09-SP2 export LD_LIBRARY_PATH=/home/synopsys/verdi/Verdi_O-2018.09-SP2/share/PLI/VCS/LINUX64 export VERDI_HOME=/home/synopsys/verdi/Verdi_O-2018.09-SP2 export SCL_HOME=/home/synopsys/scl/2018.06 #dve PATH=$PATH:$VCS_HOME/gui/dve/bin alias dve="dve" #VCS PATH=$PATH:$VCS_HOME/bin alias vcs="vcs" #VERDI PATH=$PATH:$VERDI_HOME/bin alias verdi="verdi" #scl PATH=$PATH:$SCL_HOME/linux64/bin export VCS_ARCH_OVERRIDE=linux #LICENCE export LM_LICENSE_FILE=27000@localhost.localdomain alias lmg_synopsys="lmgrd -c /home/synopsys/scl/2018.06/admin/license/Synopsys.dat"3)激活先使用以下命令设置开放端口:firewall-cmd --zone=public --add-port=27000/tcp --permanentfirewall-cmd --reload然后在输入“lmg_synopsys”进行激活,这个每次启动虚拟机都需要这样操作一下。但是这里提示缺少依赖库。输入以下命令进行安装:lmg_synopsysyum install redhat-lsb.i686激活好后输入“verdi”打开verdi工具,查看是否激活成功,但是这儿有是有错误,使用下面命令进行安装,成功后再输入“verdi”,能够打开verdi,激活成功sudo yum install libpng12 -y4.测试工程使用以下命令将12文件下的ic_pro.tar解压在home目录下,然后进入到工程的仿真目录下,用gvim打开make脚本,这个就是仿真的脚本。tar -xf ./12/ic_pro.tarcd ic_pro/heart/sim/输入以下命令进行仿真,make vcsmake verdi如果有错误提示:gcc: Command not found。需要安装一下gcc,但是也会有其他问题,一般可能是环境和license有问题,需要仔细去核对一下。使用以下命令安装gcc:yum -y update gccyum -y install gcc+ gcc-c++仿真的效果如下,使用verdi查看波形,这个工程可以看我这篇文章: 来自:https://bbs.eetop.cn/thread-895489-1-1.htmlps:本文章自做笔记记录,个人不推荐,现在开源工具也很发达,个人学习使用可以使用开源工具。

EDA-IC设计平台 Synopsys tools套装 VCS2018 Verdi2018 链接: https://pan.baidu.com/s/1pcuTqFEkMmgndafvnhlzlA 提取码: cm7e 复制这段内容后打开百度网盘手机App,操作更方便哦 --来自百度网盘超级会员v3的分享安装好的EDA环境,解压可以直接使用:环境为vmware虚拟机;解压后,使用vmware打开启动,选择“我已移动”,有问题可以联系我。链接: https://pan.baidu.com/s/1lvp4WUzRCQIZmHM8wrHSyw 提取码: 8q4c 复制这段内容后打开百度网盘手机App,操作更方便哦 --来自百度网盘超级会员v3的分享账户root密码:2020License到2030年安装1)安装installer提示:教程非本人所写,稍有改动,原文详见图片logo进入到synopsysinstaller_v5.0目录下,先运行.run文件,然后提示你输入安装路径,默认回车在当下目录就行;完成后直接运行生成的setup.sh文件。但是会出现如下error。sudo ./SynopsysInstaller_v5.0.run./setup.sh这个问题应该是缺少依赖库,先查找这个库出自那个安装包,然后进行安装。安装过程中会有提示,输入“y”回车就行。repoquery --nvr --whatprovides libXss.so.1sudo yum install libXScrnSaver-1.2.2-6.1.el7依赖库安装好后,再次运行 “./setup.sh”就会出现安装界面了。2)安装IC软件进入到home目录下,新建synopsys的文件夹,以后synopsys的软件均安装在这个目录下;home不是在普通用户下,需要超级用户权限,而软件安装必须在普通用户下所以需要将这个文件加权限打开;sudo mkdir synopsyssudo chmod 777 synopsys然后回到install目录下,运行“./setup.sh”开始安装,点击start;默认,点击next。这里需要选择安装包的路径,我们先安装scl,选择好点击ok;这里选择我们安装路径,选择我们上面新建的synopsys目录下。全部选上,next。安装确认,没有问题点击next;点击接受并安装,安装完成点击 Finish,然后点击Dismiss完成;其他synopsys软件也是这样步骤,依次安装完就行!4.license生成、环境以及激活1)启动scl_keygen生成器这个需要在window下进行,双击运行scl_keygen.exe.需要填写这4项信息,HOST ID Daemon 和HOST ID Feature填写一样的,Port选择27000。进入虚拟机,打开terminal使用以下命令查找hostnameifconfig我的填写如下,然后点击Generate生成license打开生成licens文件,修改第二行,这个需要与虚拟机里面scl路径一致,不然license无效。修改好后把这个文件复制到共享文件中。这个文件最后需要放到这个“scl/2018.06/admin/license/”目录下,要与环境里面设置的路径一致。2)环境设置打开.bashrc环境文件,加入以下内容,对应自己安装路径。但是需要注意倒数第二行,需要确认主机名是否正确。保存退出,source一下。export DVE_HOME=/home/synopsys/vcs/O-2018.09-SP2 export VCS_HOME=/home/synopsys/vcs/O-2018.09-SP2 export VCS_MX_HOME=/home/synopsys/vcs-mx/O-2018.09-SP2 export LD_LIBRARY_PATH=/home/synopsys/verdi/Verdi_O-2018.09-SP2/share/PLI/VCS/LINUX64 export VERDI_HOME=/home/synopsys/verdi/Verdi_O-2018.09-SP2 export SCL_HOME=/home/synopsys/scl/2018.06 #dve PATH=$PATH:$VCS_HOME/gui/dve/bin alias dve="dve" #VCS PATH=$PATH:$VCS_HOME/bin alias vcs="vcs" #VERDI PATH=$PATH:$VERDI_HOME/bin alias verdi="verdi" #scl PATH=$PATH:$SCL_HOME/linux64/bin export VCS_ARCH_OVERRIDE=linux #LICENCE export LM_LICENSE_FILE=27000@localhost.localdomain alias lmg_synopsys="lmgrd -c /home/synopsys/scl/2018.06/admin/license/Synopsys.dat"3)激活先使用以下命令设置开放端口:firewall-cmd --zone=public --add-port=27000/tcp --permanentfirewall-cmd --reload然后在输入“lmg_synopsys”进行激活,这个每次启动虚拟机都需要这样操作一下。但是这里提示缺少依赖库。输入以下命令进行安装:lmg_synopsysyum install redhat-lsb.i686激活好后输入“verdi”打开verdi工具,查看是否激活成功,但是这儿有是有错误,使用下面命令进行安装,成功后再输入“verdi”,能够打开verdi,激活成功sudo yum install libpng12 -y4.测试工程使用以下命令将12文件下的ic_pro.tar解压在home目录下,然后进入到工程的仿真目录下,用gvim打开make脚本,这个就是仿真的脚本。tar -xf ./12/ic_pro.tarcd ic_pro/heart/sim/输入以下命令进行仿真,make vcsmake verdi如果有错误提示:gcc: Command not found。需要安装一下gcc,但是也会有其他问题,一般可能是环境和license有问题,需要仔细去核对一下。使用以下命令安装gcc:yum -y update gccyum -y install gcc+ gcc-c++仿真的效果如下,使用verdi查看波形,这个工程可以看我这篇文章: 来自:https://bbs.eetop.cn/thread-895489-1-1.htmlps:本文章自做笔记记录,个人不推荐,现在开源工具也很发达,个人学习使用可以使用开源工具。 -

vcs排除覆盖率虚高的方法 Synopsys vcs仿真器在收集覆盖率是怎么排除仿真glitch产生的覆盖率数据?在Synopsys VCS仿真器中,可以通过设置一些选项和参数来排除仿真glitch产生的覆盖率数据。以下是一些建议:使用-coverage exclude_glblck glitch选项:此选项将忽略由于glitch引起的全局时钟块的覆盖率。设置适当的仿真步长:使用较小的仿真步长可能会导致更多的glitch。尝试增加仿真步长以减少glitch的可能性。使用-vcs+lic+nowarn+assert选项:此选项会关闭所有警告,并启用所有的断言。这有助于捕获可能导致glitch的错误条件。调整覆盖率收集频率:通过调整-cm linecover或-cm togglecover等选项的频率,可以减少glitch的影响。在代码中添加额外的检查:如果可能,可以在设计代码中添加额外的检查,以确保信号稳定后再进行覆盖率收集。分析覆盖率报告:查看覆盖率报告并识别哪些区域可能存在glitch。然后,可以在这些区域中添加额外的测试用例,以更好地覆盖这些情况。请注意,这些方法可能无法完全消除由glitch引起的覆盖率数据问题,但它们可以帮助减少此类问题的发生。在Synopsys VCS仿真器中,排除由于glitch(瞬时信号跳变)产生的覆盖率数据可以通过使用特定的编译和仿真选项来实现。以下是一些方法,这些方法基于上述文档中的信息:1.使用-cm_glitch选项:这个选项可以用来过滤掉由于glitch导致的额外夏盖率数据。例如,设置-cm_glitch 0可以过滤掉在0时刻由于glitchi产生的夏盖率数据。2.利用$cm_coverage系统函数:在Verilog:或SystemVerilog代码中,可以通过$cm_coverage系统函数动态地查询或修改夏盖率选项。这个函数可以用来在运行时使能或关闭特定的夏盖率类型,从而避免收集由于gtch产生的夏盖率数据3。3.设置-covg_cont_on_error选项:当仿真运行到非法功能夏盖率bin时,使用这个选项可以让仿真继续运行,而不是停止。这样可以避免由于错误或异常情况导致的覆盖率数据被错误地收集。通过上述方法,用户可以有效地排除由于gtc产生的夏盖率数据,确保覆盖率结果的准确性和可靠性。这些选项和函数提供了灵活性,使得覆盖率收集可以专注于用户感兴趣的特定仿真行为和事件,同时避免由于仿真过程中的瞬时信号跳变而引入的噪声。Synopsys vcs仿真器在收集覆盖率是怎么排除仿真0时刻的覆盖率数据在Synopsys VCS仿真器中,可以通过以下方法来排除仿真0时刻的覆盖率数据:使用-cm_init选项:此选项允许您指定一个时间点(以模拟周期为单位),从该时间点开始收集覆盖率数据。例如,如果您希望从第一个时钟边沿开始收集覆盖率数据,可以使用以下命令:-cm_init=1这将忽略仿真开始时的0时刻覆盖率数据。使用条件覆盖率:您可以使用条件覆盖率(CCOV)选项来控制何时开始收集覆盖率数据。通过在设计代码中添加相应的条件语句,可以在满足特定条件后开始收集覆盖率数据。例如:initial begin @(posedge clk); if (reset == 1'b0) begin $set_coverage_control("start"); end end在代码中添加额外的检查:如果可能,可以在设计代码中添加额外的检查,以确保信号稳定后再进行覆盖率收集。这可以帮助避免在仿真开始时收集不准确的覆盖率数据。请注意,这些方法可能无法完全消除由仿真0时刻引起的覆盖率数据问题,但它们可以帮助减少此类问题的发生。当然,以下是更多关于如何在Synopsys VCS仿真器中排除仿真0时刻的覆盖率数据的方法:使用延迟初始化(Deferred Initialization):通过使用VCS的延迟初始化功能,可以在仿真开始时避免某些模块或信号被初始化。这可以帮助确保在收集覆盖率数据之前,所有必要的信号和模块都已经稳定。分析覆盖率报告:查看覆盖率报告并识别哪些区域可能存在由于仿真0时刻导致的问题。然后,可以针对这些区域编写额外的测试用例,以更好地覆盖这些情况。使用-cm_control选项:此选项允许您控制何时开始和停止收集覆盖率数据。您可以根据需要创建多个覆盖组,并为每个组设置不同的起始和结束时间点。例如:-cm_control "start_group1:2; end_group1:3" -cm_control "start_group2:5; end_group2:7"调整仿真步长:尝试增加仿真步长以减少由仿真0时刻引起的不准确的覆盖率数据。验证设计代码:检查您的设计代码,确保在仿真开始时没有触发任何不应发生的事件或状态变化。这可能包括复位、中断或其他可能导致覆盖率数据问题的条件。请记住,这些方法可能会有所帮助,但可能无法完全消除由仿真0时刻引起的覆盖率数据问题。在实际应用中,您可能需要结合多种方法来优化覆盖率数据的质量。在Synopsys VCS仿真器中,排除仿真0时刻的夏盖率数据可以通过设置特定的编译和仿真选项来实现。以下是一些方法和选项,这些方法基于上述文档中的信息:1.使用编译选项-cmhier来指定要收集覆盖率的模块、实例和子层次结构,以及要排除的源文件。例如,如果你想排除某个模块及其子模块的夏盖率,可以在-cm_hier配置文件中使用+tree instance_name[level_number]来指定只编译和收集夏盖率的实例和子实例,而忽略其他实例1。2.利用仿真选项-cm来控制覆盖率的收集。例如,如果你想排除0时刻的某些wys块的夏盖率,可以通过设置-cm选项来指定不收集特定类型的覆盖率,如tg1(翻转覆盖率)或1ine(代码行覆盖本)3.使用系统函数$cm_coverage()在仿真过程中动态地开启或关闭覆盖率的收集。通过在仿真脚本中设置条件,可以在0时刻之后开启夏盖率收集,从而排除0时刻的覆盖率数据1。4.在仿真脚本中设置条件,以确保在0时刻不执行某些测试用例或测试序列,这样可以避免在0时刻收集到不希望的夏盖率数据。5.使用urg命令行工具来合并覆盖率数据时,可以通过-dbname选项指定要合并的覆盖率数据库文件,而不包括0时刻的数据。此外,可以使用-orep0rt选项来阻止生成包含0时刻数据的夏盖率报告。通过上述方法,用户可以根据需要排除仿真0时刻的夏盖率数据,以便更准确地分析和评估仿真结果。这些方法提供了灵活性,使得覆盖率收集可以专注于用户感兴趣的特定仿真行为和事件。

vcs排除覆盖率虚高的方法 Synopsys vcs仿真器在收集覆盖率是怎么排除仿真glitch产生的覆盖率数据?在Synopsys VCS仿真器中,可以通过设置一些选项和参数来排除仿真glitch产生的覆盖率数据。以下是一些建议:使用-coverage exclude_glblck glitch选项:此选项将忽略由于glitch引起的全局时钟块的覆盖率。设置适当的仿真步长:使用较小的仿真步长可能会导致更多的glitch。尝试增加仿真步长以减少glitch的可能性。使用-vcs+lic+nowarn+assert选项:此选项会关闭所有警告,并启用所有的断言。这有助于捕获可能导致glitch的错误条件。调整覆盖率收集频率:通过调整-cm linecover或-cm togglecover等选项的频率,可以减少glitch的影响。在代码中添加额外的检查:如果可能,可以在设计代码中添加额外的检查,以确保信号稳定后再进行覆盖率收集。分析覆盖率报告:查看覆盖率报告并识别哪些区域可能存在glitch。然后,可以在这些区域中添加额外的测试用例,以更好地覆盖这些情况。请注意,这些方法可能无法完全消除由glitch引起的覆盖率数据问题,但它们可以帮助减少此类问题的发生。在Synopsys VCS仿真器中,排除由于glitch(瞬时信号跳变)产生的覆盖率数据可以通过使用特定的编译和仿真选项来实现。以下是一些方法,这些方法基于上述文档中的信息:1.使用-cm_glitch选项:这个选项可以用来过滤掉由于glitch导致的额外夏盖率数据。例如,设置-cm_glitch 0可以过滤掉在0时刻由于glitchi产生的夏盖率数据。2.利用$cm_coverage系统函数:在Verilog:或SystemVerilog代码中,可以通过$cm_coverage系统函数动态地查询或修改夏盖率选项。这个函数可以用来在运行时使能或关闭特定的夏盖率类型,从而避免收集由于gtch产生的夏盖率数据3。3.设置-covg_cont_on_error选项:当仿真运行到非法功能夏盖率bin时,使用这个选项可以让仿真继续运行,而不是停止。这样可以避免由于错误或异常情况导致的覆盖率数据被错误地收集。通过上述方法,用户可以有效地排除由于gtc产生的夏盖率数据,确保覆盖率结果的准确性和可靠性。这些选项和函数提供了灵活性,使得覆盖率收集可以专注于用户感兴趣的特定仿真行为和事件,同时避免由于仿真过程中的瞬时信号跳变而引入的噪声。Synopsys vcs仿真器在收集覆盖率是怎么排除仿真0时刻的覆盖率数据在Synopsys VCS仿真器中,可以通过以下方法来排除仿真0时刻的覆盖率数据:使用-cm_init选项:此选项允许您指定一个时间点(以模拟周期为单位),从该时间点开始收集覆盖率数据。例如,如果您希望从第一个时钟边沿开始收集覆盖率数据,可以使用以下命令:-cm_init=1这将忽略仿真开始时的0时刻覆盖率数据。使用条件覆盖率:您可以使用条件覆盖率(CCOV)选项来控制何时开始收集覆盖率数据。通过在设计代码中添加相应的条件语句,可以在满足特定条件后开始收集覆盖率数据。例如:initial begin @(posedge clk); if (reset == 1'b0) begin $set_coverage_control("start"); end end在代码中添加额外的检查:如果可能,可以在设计代码中添加额外的检查,以确保信号稳定后再进行覆盖率收集。这可以帮助避免在仿真开始时收集不准确的覆盖率数据。请注意,这些方法可能无法完全消除由仿真0时刻引起的覆盖率数据问题,但它们可以帮助减少此类问题的发生。当然,以下是更多关于如何在Synopsys VCS仿真器中排除仿真0时刻的覆盖率数据的方法:使用延迟初始化(Deferred Initialization):通过使用VCS的延迟初始化功能,可以在仿真开始时避免某些模块或信号被初始化。这可以帮助确保在收集覆盖率数据之前,所有必要的信号和模块都已经稳定。分析覆盖率报告:查看覆盖率报告并识别哪些区域可能存在由于仿真0时刻导致的问题。然后,可以针对这些区域编写额外的测试用例,以更好地覆盖这些情况。使用-cm_control选项:此选项允许您控制何时开始和停止收集覆盖率数据。您可以根据需要创建多个覆盖组,并为每个组设置不同的起始和结束时间点。例如:-cm_control "start_group1:2; end_group1:3" -cm_control "start_group2:5; end_group2:7"调整仿真步长:尝试增加仿真步长以减少由仿真0时刻引起的不准确的覆盖率数据。验证设计代码:检查您的设计代码,确保在仿真开始时没有触发任何不应发生的事件或状态变化。这可能包括复位、中断或其他可能导致覆盖率数据问题的条件。请记住,这些方法可能会有所帮助,但可能无法完全消除由仿真0时刻引起的覆盖率数据问题。在实际应用中,您可能需要结合多种方法来优化覆盖率数据的质量。在Synopsys VCS仿真器中,排除仿真0时刻的夏盖率数据可以通过设置特定的编译和仿真选项来实现。以下是一些方法和选项,这些方法基于上述文档中的信息:1.使用编译选项-cmhier来指定要收集覆盖率的模块、实例和子层次结构,以及要排除的源文件。例如,如果你想排除某个模块及其子模块的夏盖率,可以在-cm_hier配置文件中使用+tree instance_name[level_number]来指定只编译和收集夏盖率的实例和子实例,而忽略其他实例1。2.利用仿真选项-cm来控制覆盖率的收集。例如,如果你想排除0时刻的某些wys块的夏盖率,可以通过设置-cm选项来指定不收集特定类型的覆盖率,如tg1(翻转覆盖率)或1ine(代码行覆盖本)3.使用系统函数$cm_coverage()在仿真过程中动态地开启或关闭覆盖率的收集。通过在仿真脚本中设置条件,可以在0时刻之后开启夏盖率收集,从而排除0时刻的覆盖率数据1。4.在仿真脚本中设置条件,以确保在0时刻不执行某些测试用例或测试序列,这样可以避免在0时刻收集到不希望的夏盖率数据。5.使用urg命令行工具来合并覆盖率数据时,可以通过-dbname选项指定要合并的覆盖率数据库文件,而不包括0时刻的数据。此外,可以使用-orep0rt选项来阻止生成包含0时刻数据的夏盖率报告。通过上述方法,用户可以根据需要排除仿真0时刻的夏盖率数据,以便更准确地分析和评估仿真结果。这些方法提供了灵活性,使得覆盖率收集可以专注于用户感兴趣的特定仿真行为和事件。