搜索到

3

篇与

的结果

-

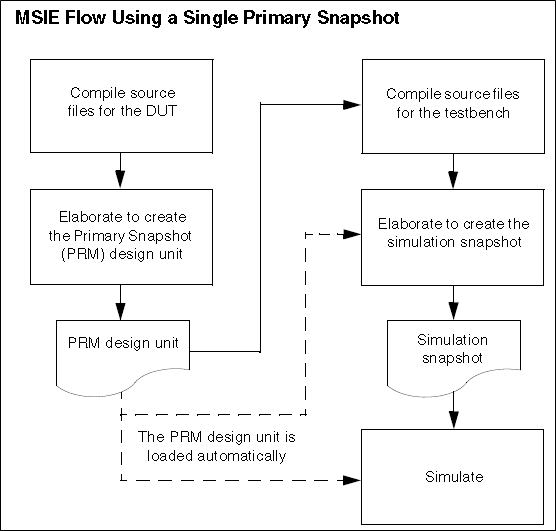

cadence-irun(xrun) 增量编译 irun支持MSIE编译,MSIE的全称是 multi-snapshot incremental elaboration。将多个编译好的snapshot,组合成一个最终的snapshot,去仿真。利用这个技术,我们就可以使用irun来进行增量编译,从而节约编译时间。为了实现增量编译,我们将snapshot分为primary snapshot和incremental snapshot,primary snapshot指环境中不经常变化的代码,编译成的snapshot,incremental snapshot指环境中经常变化的代码,编译成的snapshot,最后再将这两个snapshot进行组合,得到最终的snapshot,去仿真。一、编译流程下图是单个primary snapshot的编译流程:将DUT,编译成primary snapshot,TB载入primary snapshot后,和tb一起进行编译,得到仿真的snapshot,再去仿真。下图是多个primary snapshot的编译流程:将SOC编译成primary snapshot,将IP编译成primary snapshot,将2个primary snapshot,和tb一起编译,得到最终的仿真snapshot,再进行仿真。二、实现方法一般情况下,我们是将DUT和TB进行分开编译,以实现增量编译。对于验证人员来说,DUT是不会变化的,因此我们可以将DUT,编译成primary snapshot,TB部分载入DUT的primary snapshot,和自己的TB代码一起编译,成最终的incremental snapshot,去仿真。这样,当环境修改之后,不需要重新编译RTL,这样,就节省了编译时间。特别是RTL的设计规模很大之后,这节约的时间,就更明显了。三、测试测试环境,组织结构如下:flist.rtl : 编译rtl的flistflist.tb : 编译tb的flistMakefiletop_tb.sv : testbench顶层source: 存放rtl code的目录uvm_code:存放tb code的目录1、makefile解析 Makefile内容如下:tc:= base_test_0 irun_prim: irun -sv -64bit -f flist.rtl -mkprimsnap -top uart_tx -l irun_rtl.log irun_inca: irun -c -sv -64bit -f flist.tb -uvm -uvmhome CDNS-1.2 -primtop uart_tx -l irun_tb.log irun_run: irun -R +UVM_TESTNAME=$(tc) -l irun_run.log clean: rm -rf INCA_libs rm -f *.log 对于 irun_prim 目标,根据RTL代码生成primary snapshot。-sv: 启动sv编译-64bit: 启动64位的irun-f flist.rtl : 指定编译RTL的flist-mkprimsnap: 生成primary snapshot-top: 指定RTL的顶层-l: 指定log文件对于 irun_inca 目标,载入RTL编译得到的primary snapshot,根据TB代码生成incremental snapshot, -c: 只编译,不仿真-f flist.tb: 指定编译TB的flist-uvm: 启动uvm编译-uvmhome CDNS-1.2: 指定uvm的home目录为irun工具目录下的UVM-1.2目录-primtop uart_tx: 指定需要载入primary snapshot的顶层。对于 irun_run 目标,仿真。-R : 不编译,直接仿真+UVM_TESTNAME: uvm指定testcase的选项2、第一次执行make irun_prim; 生成primary snapshotmake irun_inca: 载入primary snapshot,和tb一起编译生成incremantal snapshot。载入primary snapshot:生成incremantal snapshot。3、第二次执行此时,修改top_tb.sv的代码,增加一行打印。因为RTL没有编译,因此可以跳过编译RTL,直接make irun_inca。载入 primary snapshot,跳过了代码生成。生成incremantal snapshot。仿真,打印出hello。测试的RTL,规模比较小,感受不到增量编译的好处,但是当RTL的规模一旦变得很大,编译RTL就要花费数十分钟,此时,就可以体会到增量编译的好处了。在服务器,测试我们的环境,使用增量编译后,将编译时间,从5分钟,缩减到了20秒。https://www.cnblogs.com/david-wei0810/p/14177607.html

cadence-irun(xrun) 增量编译 irun支持MSIE编译,MSIE的全称是 multi-snapshot incremental elaboration。将多个编译好的snapshot,组合成一个最终的snapshot,去仿真。利用这个技术,我们就可以使用irun来进行增量编译,从而节约编译时间。为了实现增量编译,我们将snapshot分为primary snapshot和incremental snapshot,primary snapshot指环境中不经常变化的代码,编译成的snapshot,incremental snapshot指环境中经常变化的代码,编译成的snapshot,最后再将这两个snapshot进行组合,得到最终的snapshot,去仿真。一、编译流程下图是单个primary snapshot的编译流程:将DUT,编译成primary snapshot,TB载入primary snapshot后,和tb一起进行编译,得到仿真的snapshot,再去仿真。下图是多个primary snapshot的编译流程:将SOC编译成primary snapshot,将IP编译成primary snapshot,将2个primary snapshot,和tb一起编译,得到最终的仿真snapshot,再进行仿真。二、实现方法一般情况下,我们是将DUT和TB进行分开编译,以实现增量编译。对于验证人员来说,DUT是不会变化的,因此我们可以将DUT,编译成primary snapshot,TB部分载入DUT的primary snapshot,和自己的TB代码一起编译,成最终的incremental snapshot,去仿真。这样,当环境修改之后,不需要重新编译RTL,这样,就节省了编译时间。特别是RTL的设计规模很大之后,这节约的时间,就更明显了。三、测试测试环境,组织结构如下:flist.rtl : 编译rtl的flistflist.tb : 编译tb的flistMakefiletop_tb.sv : testbench顶层source: 存放rtl code的目录uvm_code:存放tb code的目录1、makefile解析 Makefile内容如下:tc:= base_test_0 irun_prim: irun -sv -64bit -f flist.rtl -mkprimsnap -top uart_tx -l irun_rtl.log irun_inca: irun -c -sv -64bit -f flist.tb -uvm -uvmhome CDNS-1.2 -primtop uart_tx -l irun_tb.log irun_run: irun -R +UVM_TESTNAME=$(tc) -l irun_run.log clean: rm -rf INCA_libs rm -f *.log 对于 irun_prim 目标,根据RTL代码生成primary snapshot。-sv: 启动sv编译-64bit: 启动64位的irun-f flist.rtl : 指定编译RTL的flist-mkprimsnap: 生成primary snapshot-top: 指定RTL的顶层-l: 指定log文件对于 irun_inca 目标,载入RTL编译得到的primary snapshot,根据TB代码生成incremental snapshot, -c: 只编译,不仿真-f flist.tb: 指定编译TB的flist-uvm: 启动uvm编译-uvmhome CDNS-1.2: 指定uvm的home目录为irun工具目录下的UVM-1.2目录-primtop uart_tx: 指定需要载入primary snapshot的顶层。对于 irun_run 目标,仿真。-R : 不编译,直接仿真+UVM_TESTNAME: uvm指定testcase的选项2、第一次执行make irun_prim; 生成primary snapshotmake irun_inca: 载入primary snapshot,和tb一起编译生成incremantal snapshot。载入primary snapshot:生成incremantal snapshot。3、第二次执行此时,修改top_tb.sv的代码,增加一行打印。因为RTL没有编译,因此可以跳过编译RTL,直接make irun_inca。载入 primary snapshot,跳过了代码生成。生成incremantal snapshot。仿真,打印出hello。测试的RTL,规模比较小,感受不到增量编译的好处,但是当RTL的规模一旦变得很大,编译RTL就要花费数十分钟,此时,就可以体会到增量编译的好处了。在服务器,测试我们的环境,使用增量编译后,将编译时间,从5分钟,缩减到了20秒。https://www.cnblogs.com/david-wei0810/p/14177607.html -

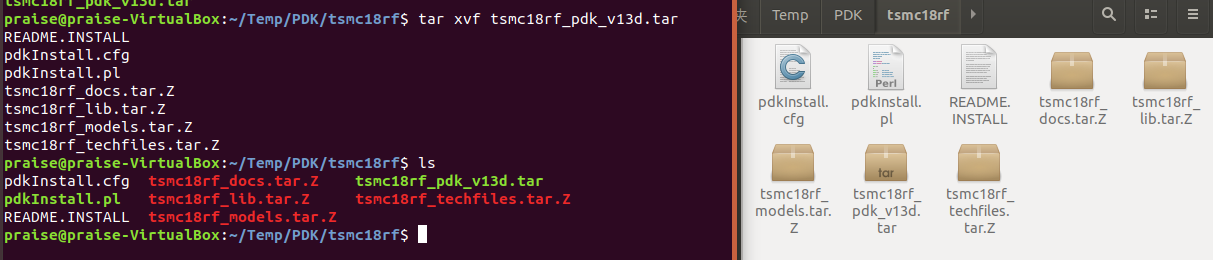

cadence virtuoso安装tsmc8rf 注意1:可以直接下载免安装OA 格式的tsmc18rf库,下载路径:https://download.csdn.net/download/d_pcb66/87074114注意2:IC617 之后的virtuoso版本不再提供cdb2oa功能会提示错误;ERROR (CDBOA-2003):Support for the CDB to OpenAccess translator has been removed. Contact Cadence Customer Support to discuss how to complete any outstanding migration tasks.tsmc18rf 工艺库可从如下地址下载https://download.csdn.net/download/qq_35379940/11953193下载后得到文件 tsmc18rf_pdk_v13d.tar,将该文件放入单独的文件夹中,然后解压,可得到如下的一些文件。对于不同的工程,通常会采用不同的工艺和工艺库,因此把 PDK 安装在工程目录下。之前创建了 project01 作为测试,现在把这个工艺库安装在这个目录下。在 tsmc18rf 工艺库解压目录下直接执行如下语句进行安装。perl pdkInstall.pl其中 1P6M 指工艺为 1 层多晶硅 6 层金属。 由于 IC610 以上的版本只能识别 OA 格式的 PDK,而 tsmc18rf 采用的是 CDB 格式,因此需要用 IC617 自带的工具进行转换。执行以下指令为转换做准备。cd /home/praise/ICDesign/project01mkdir OAconvertmkdir OAconvert/cdbcp /home/praise/ICDesign/project01/tsmc18rf_1P6M/cds.lib OAconvert/cdb编辑 OAconvert/cdb/cds.lib 文件,删除前两行,将第三行改为如下形式,指向 CDB 格式的 PDK。DEFINE tsmc18rf /home/praise/ICDesign/project01/tsmc18rf_1P6M/tsmc18rf进入 OAconvert 文件夹,运行 virtuoso。cd OAconvertrun_virtuoso在下图中点击 Browse,选择刚才修改的 cds.lib 文件,如下图红框中所示,然后点击 OK。稍等一会儿,等运行完成后,用 OAconvert 中生成的 tsmc18rf 替换原本 tsmc18rf_1P6M 文件夹中的同名文件。注意此过程可能会有三个报错,如下图 log 文件所示,感谢 zli_网友的提醒,发现此处是由于缺少 libXp.so.6 动态链接库所致,cdb2oail 程序需要 libXp.so.6 才能运行,但 ubuntu18.04 中删除了该库,从而导致此错误。解决办法是,下载下面的 deb 安装包,然后用 dpkg 命令安装。sudo dpkg -i libxp6_1.0.2-2_amd64.deblibxp6_1.0.2-2_amd64.deb安装完成后重启 virtuoso 重新进行转换,就不会报错了。 打开上面图中生成的 tsmc18rf 文件夹,找到 libInit.il 文件,将下面两行注释掉。然后打开 /home/praise/ICDesign/project01/tsmc18rf_1P6M/techfile,将文件中最后一段 Controls 剪切到最前面,如下图所示。 退出 virtuoso,回到之前的 project01 文件夹,重新运行 run_virtuoso。cd /home/praise/ICDesign/project01run_virtuoso新建 Library,Name 为 tsmc18rf,点击 OK。等待运行完成即可。

cadence virtuoso安装tsmc8rf 注意1:可以直接下载免安装OA 格式的tsmc18rf库,下载路径:https://download.csdn.net/download/d_pcb66/87074114注意2:IC617 之后的virtuoso版本不再提供cdb2oa功能会提示错误;ERROR (CDBOA-2003):Support for the CDB to OpenAccess translator has been removed. Contact Cadence Customer Support to discuss how to complete any outstanding migration tasks.tsmc18rf 工艺库可从如下地址下载https://download.csdn.net/download/qq_35379940/11953193下载后得到文件 tsmc18rf_pdk_v13d.tar,将该文件放入单独的文件夹中,然后解压,可得到如下的一些文件。对于不同的工程,通常会采用不同的工艺和工艺库,因此把 PDK 安装在工程目录下。之前创建了 project01 作为测试,现在把这个工艺库安装在这个目录下。在 tsmc18rf 工艺库解压目录下直接执行如下语句进行安装。perl pdkInstall.pl其中 1P6M 指工艺为 1 层多晶硅 6 层金属。 由于 IC610 以上的版本只能识别 OA 格式的 PDK,而 tsmc18rf 采用的是 CDB 格式,因此需要用 IC617 自带的工具进行转换。执行以下指令为转换做准备。cd /home/praise/ICDesign/project01mkdir OAconvertmkdir OAconvert/cdbcp /home/praise/ICDesign/project01/tsmc18rf_1P6M/cds.lib OAconvert/cdb编辑 OAconvert/cdb/cds.lib 文件,删除前两行,将第三行改为如下形式,指向 CDB 格式的 PDK。DEFINE tsmc18rf /home/praise/ICDesign/project01/tsmc18rf_1P6M/tsmc18rf进入 OAconvert 文件夹,运行 virtuoso。cd OAconvertrun_virtuoso在下图中点击 Browse,选择刚才修改的 cds.lib 文件,如下图红框中所示,然后点击 OK。稍等一会儿,等运行完成后,用 OAconvert 中生成的 tsmc18rf 替换原本 tsmc18rf_1P6M 文件夹中的同名文件。注意此过程可能会有三个报错,如下图 log 文件所示,感谢 zli_网友的提醒,发现此处是由于缺少 libXp.so.6 动态链接库所致,cdb2oail 程序需要 libXp.so.6 才能运行,但 ubuntu18.04 中删除了该库,从而导致此错误。解决办法是,下载下面的 deb 安装包,然后用 dpkg 命令安装。sudo dpkg -i libxp6_1.0.2-2_amd64.deblibxp6_1.0.2-2_amd64.deb安装完成后重启 virtuoso 重新进行转换,就不会报错了。 打开上面图中生成的 tsmc18rf 文件夹,找到 libInit.il 文件,将下面两行注释掉。然后打开 /home/praise/ICDesign/project01/tsmc18rf_1P6M/techfile,将文件中最后一段 Controls 剪切到最前面,如下图所示。 退出 virtuoso,回到之前的 project01 文件夹,重新运行 run_virtuoso。cd /home/praise/ICDesign/project01run_virtuoso新建 Library,Name 为 tsmc18rf,点击 OK。等待运行完成即可。 -

cadence upf低功耗流程的仿真验证 本文是记录项目过程中遇到的奇巧淫技,如有遗漏或者不足,请大家改正和补充,谢谢。随着深亚微米技术的普及与发展,leakage功耗在整个功耗中的比重越来越大,比如45nm下,已经占到了60%以上,所以低功耗解决方案应运而生。目前已经有一套标准的低功耗设计流程,流程有CPF(cadence主导)和UPF(synopsys主导)两种,但技术趋势是UPF会大一统,所以本篇将为那些仍旧使用ncverilog而不是vcs仿真工具的苦逼们提供一些参考。目前常用的降低低功耗的方法有四种:多电压域、时钟门控、电源关断和动态电压频率调整。其中的时钟门控对验证影响较小,大家应该都接触过,而剩下的三个对验证工作影响较大,需要用到各个EDA厂商的低功耗解决方案。闲话就说这么多,那么cadence如何使用upf来实现低功耗流程的仿真验证呢?第一步,先得有UPF文件,根据设计需求,使用TCL建立脚本,建立和管理独立电压源、确定隔离、建立电平漂移等,一般是设计或者后端人员书写,验证工程师当然也可以写,具体内容参考IEEE 1801。第二步,仿真case中添加电源上电过程,使用$supply_on函数给相应VDD上电。第三步,将UPF嵌入到仿真命令中,即:irun -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...或者1 ncvlog ...2 ncelab -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...3 ncsim ...相关options解释如下:①-lps_1801 filename: 指定符合IEEE 1801标准的UPF文件;②-lps_assign_ft_buf: 指定assign赋值被当做buffer对待,而非默认的wire,好处是从always-on domain进入和穿过power-down domain的信号被force成x,便于debug;③-lps_const_aon: 对处在power-down domain并且直接和always-on domain相连接的tie-high或者tie-low constant,不使能corruption功能;默认不使用该功能;④-lps_enum_rand_corrupt:对于用户定义的enum类型数据,在电源关断后,随机从枚举列表中选择一个值作为变量值;和该命令相类似的还有-lps_enum_right, -lps_implicit_pso等,因为不常用,就不一一介绍了;⑤-lps_iso_verbose: 使能isolation的log功能,这个一般需要加上;⑥...其它的options请参考cadence的low-power simulation guide。最后,运行仿真即可。最后说一下low power流程验证正确性和完备性的确认方法。①增加的low power流程不能影响芯片本身功能的正确性,比如通过电源关断来降低芯片功耗,则关断再打开后,芯片还可以正常work。这部分可以利用原有的self-check验证环境来确认。②利用log文件分析,上述仿真命令-lps_verbose和UPF文件会为仿真输出与low power相关的warning, error以及assertion信息,通过log文件可以check流程的正确性;③自动的assertion checker分析,使用-lps_verify选项可以自动检查电源关断顺序(隔离->复位->断电)和电源打开过程(上电->解复位->解隔离),如不满足该时序要求,会自动报错;④利用覆盖率保证验证完备性,使用-lps_vplan选项依据UPF文件生成low power验证计划,通过simvision提供的coverage接口,得到low power相关的功能覆盖率;https://www.cnblogs.com/jyaray/p/4817777.html

cadence upf低功耗流程的仿真验证 本文是记录项目过程中遇到的奇巧淫技,如有遗漏或者不足,请大家改正和补充,谢谢。随着深亚微米技术的普及与发展,leakage功耗在整个功耗中的比重越来越大,比如45nm下,已经占到了60%以上,所以低功耗解决方案应运而生。目前已经有一套标准的低功耗设计流程,流程有CPF(cadence主导)和UPF(synopsys主导)两种,但技术趋势是UPF会大一统,所以本篇将为那些仍旧使用ncverilog而不是vcs仿真工具的苦逼们提供一些参考。目前常用的降低低功耗的方法有四种:多电压域、时钟门控、电源关断和动态电压频率调整。其中的时钟门控对验证影响较小,大家应该都接触过,而剩下的三个对验证工作影响较大,需要用到各个EDA厂商的低功耗解决方案。闲话就说这么多,那么cadence如何使用upf来实现低功耗流程的仿真验证呢?第一步,先得有UPF文件,根据设计需求,使用TCL建立脚本,建立和管理独立电压源、确定隔离、建立电平漂移等,一般是设计或者后端人员书写,验证工程师当然也可以写,具体内容参考IEEE 1801。第二步,仿真case中添加电源上电过程,使用$supply_on函数给相应VDD上电。第三步,将UPF嵌入到仿真命令中,即:irun -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...或者1 ncvlog ...2 ncelab -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...3 ncsim ...相关options解释如下:①-lps_1801 filename: 指定符合IEEE 1801标准的UPF文件;②-lps_assign_ft_buf: 指定assign赋值被当做buffer对待,而非默认的wire,好处是从always-on domain进入和穿过power-down domain的信号被force成x,便于debug;③-lps_const_aon: 对处在power-down domain并且直接和always-on domain相连接的tie-high或者tie-low constant,不使能corruption功能;默认不使用该功能;④-lps_enum_rand_corrupt:对于用户定义的enum类型数据,在电源关断后,随机从枚举列表中选择一个值作为变量值;和该命令相类似的还有-lps_enum_right, -lps_implicit_pso等,因为不常用,就不一一介绍了;⑤-lps_iso_verbose: 使能isolation的log功能,这个一般需要加上;⑥...其它的options请参考cadence的low-power simulation guide。最后,运行仿真即可。最后说一下low power流程验证正确性和完备性的确认方法。①增加的low power流程不能影响芯片本身功能的正确性,比如通过电源关断来降低芯片功耗,则关断再打开后,芯片还可以正常work。这部分可以利用原有的self-check验证环境来确认。②利用log文件分析,上述仿真命令-lps_verbose和UPF文件会为仿真输出与low power相关的warning, error以及assertion信息,通过log文件可以check流程的正确性;③自动的assertion checker分析,使用-lps_verify选项可以自动检查电源关断顺序(隔离->复位->断电)和电源打开过程(上电->解复位->解隔离),如不满足该时序要求,会自动报错;④利用覆盖率保证验证完备性,使用-lps_vplan选项依据UPF文件生成low power验证计划,通过simvision提供的coverage接口,得到low power相关的功能覆盖率;https://www.cnblogs.com/jyaray/p/4817777.html