搜索到

2

篇与

的结果

-

-

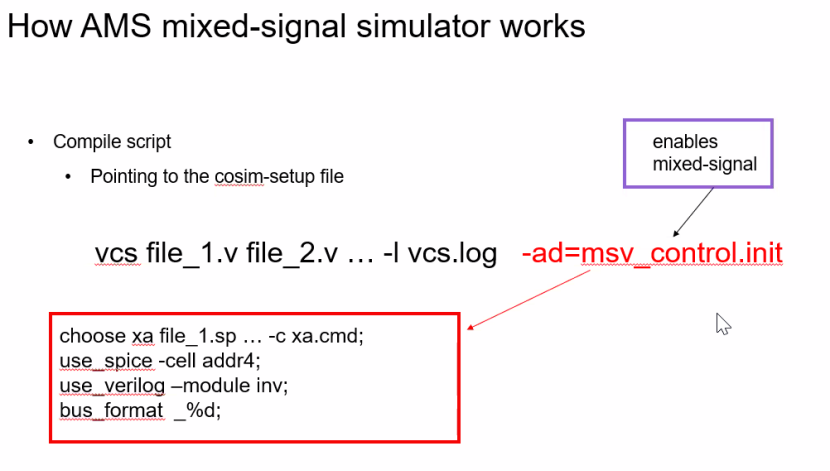

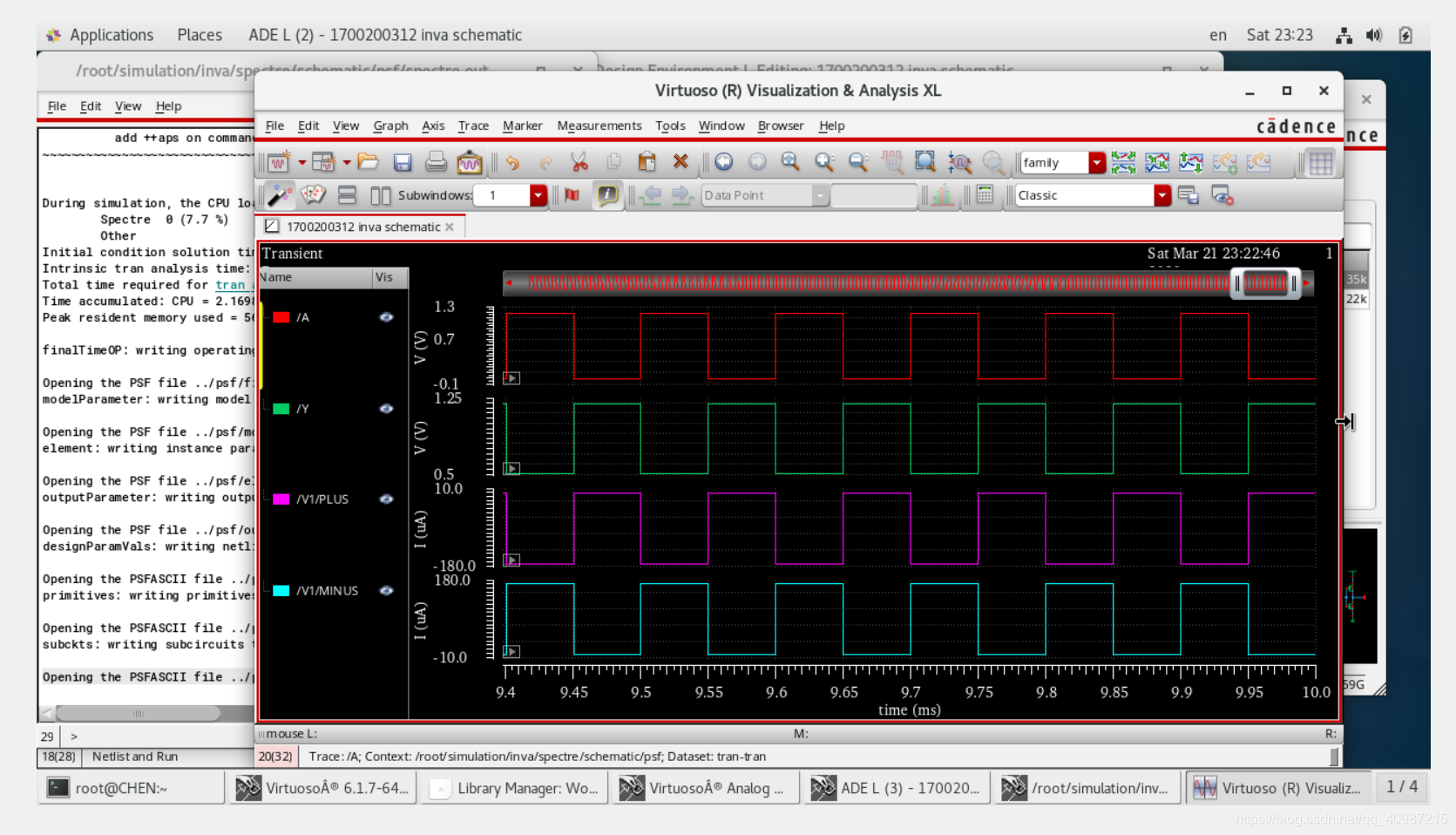

在IC617中进行xa+vcs数模混仿 基本介绍:本文档介绍了在IC617的ADE L环境的图形化界面中进行数字+模拟信号混合仿真的方法,主要分成以下几个部分:一、软件要求1、与CustomSim兼容的VCS,本文档中分别是xa2018.09和vcsmx_v2018092、Custom Waveview(波形查看软件,非必须)3、IC614或更新版本的Cadence(OA)或更新版本的IC5.1.4.1-USR5(CDBA),本文档以IC617为例。4、相应的license二、安装并设置CustomSim ADE L交互界面安装CustomSim有两种方式,分别是安装在Cadence目录中和目录外。本文档只介绍第二种方法,即安装在Cadence目录外。具体步骤如下:1、设置环境变量:setenv CDS_LOAD_ENV CSF2、在CustomSim的安装目录下找到名为CustomSim.cdsenv的文件,位置在CustomSim安装目录/ade/CustomSimADE/CustomSim.cdsenv,将其复制到home目录下。(这是CustomSim的初始化文件,不复制也无所谓)3、在home下找到.cdsinit文件并在文件中将CustomSim.ile文件的路径添加进去:Load(“CustomSim安装目录/ade/CustomSimADE/CustomSim.ile”)(这里面包含了Cadence环境下的CustomSim ADE SKILL代码)4、设置环境变量:setenv CDS_Netlisting_Mode Analog5、如果Cadence版本早于IC617且CustomSimADE版本晚于M-2017.03,则需要设置如下环境变量:setenv CDS_AUTO_64BIT ALL(在本文档中不需要进行此设置,但设置了也无妨。)6、全部设置完成后就可以按照正常的方式启动Cadence软件了。三、CustomSim ADE L的使用CustomSim ADE交互界面支持Cadence的schematic和config两种方式的设置。Schematic通常用于纯模拟仿真(CustomSim)而config通常用于混合信号仿真(CustomSim-VCS),本文档使用第二种方法。下面是设置数模混合仿真的具体步骤:1、创建原理图:新建schematic并将具体的原理图电路添加进去,模拟部分按照正常的方式创建电路并生成symbol,数字电路的创建方法有如下几种:①新建cell view,类型选择Verilog,view会自动变成functional,确定之后在里面编辑数字电路,保存并检查无误后会自动弹出生成symbol的界面,完成之后就可以用平时调用模拟电路的方法调用该模块。②大多数情况下模拟工程师并不需要写数字代码,只需要将写好的代码调用即可,此时可以用之前的方式新建verilog之后将数字代码复制进来即可。(也可以找到代码的路径将数字代码复制过去覆盖原来的代码,并修改好数字里面的module名字,重新打开该verilog再保存退出,同样可以弹出生成symbol的界面。)③CustomSim也提供了直接加载数字代码的方式,本文档不做介绍。2、创建config:创建config的名字需要和schematic相同,类型选择config,完成后会弹出一个名为New Configuration的窗口,点击view那一栏并选择schematic(唯一的选项),然后Global Bindings需要进行设置,设置之前先对各个选项做简要介绍:①Library List:Library列表,可以是Cadence自带的library,可以是工艺库,也可以是用户自定义的库,可以定义一个,也可以定义多个,如果定义多个需要用空格隔开。②View List:即之前定义过的库中所包含的view都会在里面显示。CustomSim支持的View List包括:hspiceD、spice、cmos_sch、veriloga和schematic。③Stop List:此处的内容定义了生成网表的类型,如果想生成spectre格式的网表需要在此栏填写spectre同时View List栏也需要加入spectre,如果想生成HSPICE格式的网表则需要在两栏同时填写hspiceD或者HSPICE。(注意此栏不要填错,要根据你使用的仿真器类型填写。④Constraint List:(作用不明)实际设置:可以直接点击底部的Use Template然后选择AMS并确定,实测可以成功仿真而无需额外设置,前提是使用spectre仿真。点击ok完成设置会弹出新的界面,在界面中找到ADE L选项并点击就会启动ADE界面和schematic界面。接下来的就可以关闭config界面进行下一步的设置了。四、电路设置这一步的设置方法基本与平时相同,也比较简单。1、点击Setup→Simulator/Directory/Host在弹出的界面选择CustomSim作为仿真器并确认(仿真路径可以按照自己的需求设置,不设置也可)。2、如果你之前的原理图中已经同时包含了数字和模拟模块,CustomSim就会自动选择仿真类型为混合信号仿真,无需手动设置。五、ADE环境下CustomSim的设置这一步主要是对仿真器的部分重要选项进行设置,主要是仿真器的选择和网表类型的选择。具体如下:1、在ADE L界面点击Setup→Environment会弹出设置界面:在其中可以看到Simulator Selection/Netlist Syntax/Waveform Output Format等选项。此处我们选择:CunstomSim/spectre/fsdb+fsdb(分别对应仿真器/网表/数字波形格式+模拟波形格式,波形格式可以根据自己的喜好和使用的看波形的软件设置),另外# of Cores是多核仿真选项,默认为1,如果需要加快仿真速度可以在其中填入需要的CPU的数量,如需要8颗CPU则在里面填写8(需要注意的是CPU数量并非会全部用到,仿真器会自己决定用到的数目,例如填了8,实际可能只用到了6,但不会超过8,猜测跟实际的电路复杂程度有关。)2、仿真选项设置:点击Simulation→Option→Digital,在top name栏点击Use Top Cell Name,并确定。(这一步很重要,不进行此设置仿真会无法继续)3、设置transient仿真:点击Analyses→Choose后在stop栏填入需要的仿真时间并确定。(只有tran可选)4、另外还有Model的添加,以及其它的自定义的设置再次不过多介绍。可以自行试验。六、波形保存上一步结束后就已经可以进行仿真了,但为了加快仿真速度,通常会减少保存的波形节点的数量,这一步介绍保存的方法。点击Optput→To Be Saved→Select On Design之后再原理图中依次选择需要保存的节点电压和电流,按esc完成选择。七、开始仿真Simulation→Netlist and Run开始仿真!八、常见错误及解决方法上一步中可能会有如下错误:如果模拟电路中调用了电阻且电阻是多跟串联的形式,仿真器可能会报错并提示存在器件名字和net冲突的问题,此时只需要将其中一个的名字改掉就可以了。具体方法不做赘述。九、参考文档CustomSim User Guide的CustomSim ADE Interface Integration部分。ps:仅做记录学习用,个人不推荐,仿真还是要使用自动化的命令效率才高,debug 才需要图形界面。

在IC617中进行xa+vcs数模混仿 基本介绍:本文档介绍了在IC617的ADE L环境的图形化界面中进行数字+模拟信号混合仿真的方法,主要分成以下几个部分:一、软件要求1、与CustomSim兼容的VCS,本文档中分别是xa2018.09和vcsmx_v2018092、Custom Waveview(波形查看软件,非必须)3、IC614或更新版本的Cadence(OA)或更新版本的IC5.1.4.1-USR5(CDBA),本文档以IC617为例。4、相应的license二、安装并设置CustomSim ADE L交互界面安装CustomSim有两种方式,分别是安装在Cadence目录中和目录外。本文档只介绍第二种方法,即安装在Cadence目录外。具体步骤如下:1、设置环境变量:setenv CDS_LOAD_ENV CSF2、在CustomSim的安装目录下找到名为CustomSim.cdsenv的文件,位置在CustomSim安装目录/ade/CustomSimADE/CustomSim.cdsenv,将其复制到home目录下。(这是CustomSim的初始化文件,不复制也无所谓)3、在home下找到.cdsinit文件并在文件中将CustomSim.ile文件的路径添加进去:Load(“CustomSim安装目录/ade/CustomSimADE/CustomSim.ile”)(这里面包含了Cadence环境下的CustomSim ADE SKILL代码)4、设置环境变量:setenv CDS_Netlisting_Mode Analog5、如果Cadence版本早于IC617且CustomSimADE版本晚于M-2017.03,则需要设置如下环境变量:setenv CDS_AUTO_64BIT ALL(在本文档中不需要进行此设置,但设置了也无妨。)6、全部设置完成后就可以按照正常的方式启动Cadence软件了。三、CustomSim ADE L的使用CustomSim ADE交互界面支持Cadence的schematic和config两种方式的设置。Schematic通常用于纯模拟仿真(CustomSim)而config通常用于混合信号仿真(CustomSim-VCS),本文档使用第二种方法。下面是设置数模混合仿真的具体步骤:1、创建原理图:新建schematic并将具体的原理图电路添加进去,模拟部分按照正常的方式创建电路并生成symbol,数字电路的创建方法有如下几种:①新建cell view,类型选择Verilog,view会自动变成functional,确定之后在里面编辑数字电路,保存并检查无误后会自动弹出生成symbol的界面,完成之后就可以用平时调用模拟电路的方法调用该模块。②大多数情况下模拟工程师并不需要写数字代码,只需要将写好的代码调用即可,此时可以用之前的方式新建verilog之后将数字代码复制进来即可。(也可以找到代码的路径将数字代码复制过去覆盖原来的代码,并修改好数字里面的module名字,重新打开该verilog再保存退出,同样可以弹出生成symbol的界面。)③CustomSim也提供了直接加载数字代码的方式,本文档不做介绍。2、创建config:创建config的名字需要和schematic相同,类型选择config,完成后会弹出一个名为New Configuration的窗口,点击view那一栏并选择schematic(唯一的选项),然后Global Bindings需要进行设置,设置之前先对各个选项做简要介绍:①Library List:Library列表,可以是Cadence自带的library,可以是工艺库,也可以是用户自定义的库,可以定义一个,也可以定义多个,如果定义多个需要用空格隔开。②View List:即之前定义过的库中所包含的view都会在里面显示。CustomSim支持的View List包括:hspiceD、spice、cmos_sch、veriloga和schematic。③Stop List:此处的内容定义了生成网表的类型,如果想生成spectre格式的网表需要在此栏填写spectre同时View List栏也需要加入spectre,如果想生成HSPICE格式的网表则需要在两栏同时填写hspiceD或者HSPICE。(注意此栏不要填错,要根据你使用的仿真器类型填写。④Constraint List:(作用不明)实际设置:可以直接点击底部的Use Template然后选择AMS并确定,实测可以成功仿真而无需额外设置,前提是使用spectre仿真。点击ok完成设置会弹出新的界面,在界面中找到ADE L选项并点击就会启动ADE界面和schematic界面。接下来的就可以关闭config界面进行下一步的设置了。四、电路设置这一步的设置方法基本与平时相同,也比较简单。1、点击Setup→Simulator/Directory/Host在弹出的界面选择CustomSim作为仿真器并确认(仿真路径可以按照自己的需求设置,不设置也可)。2、如果你之前的原理图中已经同时包含了数字和模拟模块,CustomSim就会自动选择仿真类型为混合信号仿真,无需手动设置。五、ADE环境下CustomSim的设置这一步主要是对仿真器的部分重要选项进行设置,主要是仿真器的选择和网表类型的选择。具体如下:1、在ADE L界面点击Setup→Environment会弹出设置界面:在其中可以看到Simulator Selection/Netlist Syntax/Waveform Output Format等选项。此处我们选择:CunstomSim/spectre/fsdb+fsdb(分别对应仿真器/网表/数字波形格式+模拟波形格式,波形格式可以根据自己的喜好和使用的看波形的软件设置),另外# of Cores是多核仿真选项,默认为1,如果需要加快仿真速度可以在其中填入需要的CPU的数量,如需要8颗CPU则在里面填写8(需要注意的是CPU数量并非会全部用到,仿真器会自己决定用到的数目,例如填了8,实际可能只用到了6,但不会超过8,猜测跟实际的电路复杂程度有关。)2、仿真选项设置:点击Simulation→Option→Digital,在top name栏点击Use Top Cell Name,并确定。(这一步很重要,不进行此设置仿真会无法继续)3、设置transient仿真:点击Analyses→Choose后在stop栏填入需要的仿真时间并确定。(只有tran可选)4、另外还有Model的添加,以及其它的自定义的设置再次不过多介绍。可以自行试验。六、波形保存上一步结束后就已经可以进行仿真了,但为了加快仿真速度,通常会减少保存的波形节点的数量,这一步介绍保存的方法。点击Optput→To Be Saved→Select On Design之后再原理图中依次选择需要保存的节点电压和电流,按esc完成选择。七、开始仿真Simulation→Netlist and Run开始仿真!八、常见错误及解决方法上一步中可能会有如下错误:如果模拟电路中调用了电阻且电阻是多跟串联的形式,仿真器可能会报错并提示存在器件名字和net冲突的问题,此时只需要将其中一个的名字改掉就可以了。具体方法不做赘述。九、参考文档CustomSim User Guide的CustomSim ADE Interface Integration部分。ps:仅做记录学习用,个人不推荐,仿真还是要使用自动化的命令效率才高,debug 才需要图形界面。