搜索到

8

篇与

的结果

-

几款免费好用的电路设计软件,你一定要试试! 果果小师弟嵌入式微处理器2022年09月16日12:01北京工程软件和在线资源往往比较昂贵,不过,对于专业人员、学生和爱好者来说是非常有益的。用户开展项目或者仅进行工程验证时,这些资源往往是必要的,但是相关成本却令许多人望而却步。今天给大家分享几款高质量的免费软件,相信你肯定喜欢!一、电路仿真PartSim网址:https://www.partsim.com/PartSim是一款基于浏览器的电路仿真器,用户可以通过该软件进行电路实验。该仿真器布局简单,从而确保易用性,同时提供完整的SPICE仿真引擎、基于Web的原理图捕获工具和图形示波器,可以监视电路的模拟/数字信号电平。该工具还包含Digi-Key BOM(物料清单),允许用户为设计组件分配零件号,然后找到分销商。▲PartSim▲PartSimEasyEDA网址:https://easyeda.com/EasyEDA旨在“通过为电子设计提供全面的数据和协作工具,帮助设计人员更快地将创意转化为制造原型”。EasyEDA提供免费的在线电路仿真、PCB设计和电子电路设计功能。人们可以访问大量的原理图元件库、PCB封装和包装、spice仿真、模型和子电路,从而节省设计时间。还可以邀请他人进行项目协作,并轻松地在团队中分享设计。标准版免费使用,并提供无限公共项目和2个私人项目。Autodesk Circuits网址:https://www.autodesk.com.cn/solutions/circuit-design-softwareAutodesk Circuits是用于电子设计和实验的一组工具。初学者可以通过Electronics Lab或Circuit Scribe开始简单的实验,而经验丰富的用户则可以直接跳至PCB设计。该软件提供大量的免费入门教程和项目教程,可以通过Electronics Lab学习。二、PCB设计DesignSpark PCB官网:https://www.rs-online.com/designspark/pcb-softwareDesignSpark PCB将自己称为世界上最易于使用的电子设计软件,专门用于快速原型设计,并且可以将你的电路想法更快地转化为可测试的电路板”。这个软件对原理图尺寸没有限制,所以用户在创建PCB设计时也没有限制。用户也可以导入和导出他们需要的任何格式的文件,并且能够以所需格式创建BOM(物料清单)。虽然该工具完全免费,但是要注意重要的一点,即用户必须在其网站上注册才能解锁程序,并且在开始工作之前必须确认所显示的广告。▲DesignSpark PCB▲DesignSpark PCB▲DesignSpark PCB▲DesignSparkPCBKiCadEDA网址:https://www.kicad.org/KiCad是一款跨平台的开源电子设计自动化套件。该套件由三个不同的工具组成:Eeschema(原理图捕捉)、PcbNEW(PCB布局)和3D Viewer(通过3D方式查看电路板设计)。其中3D Viewer是一个独特的工具,可以旋转和平移你的电路板,从而查看2D图中无法看到的细节。▲KiCad▲KiCad▲KiCad三、CAD建模FreeCAD网址:freecadweb.org/FreeCAD是一款多平台开源参数化3D建模工具,旨在帮助用户将设计项目变为现实。这是一款通用多功能工具,适合不同级别的用户。想要涉及3D打印的初学者、教育工作者或经验丰富的CAD用户都可以使用FreeCAD。程序员还可以利用Python“扩展FreeCAD的功能、用脚本实现自动化、构建自己的模块,甚至将FreeCAD嵌入到自己的应用程序中。”▲FreeCAD▲FreeCAD▲FreeCADQCAD网址:qcad.org/en/QCAD是一款免费的开源2D CAD应用程序。QCAD 是一个免费的开源应用程序,用于二维 (2D) 计算机辅助绘图 (CAD)。使用 QCAD,您可以创建技术图纸,例如建筑平面图、室内设计、机械零件或示意图和图表。QCAD 适用于 Windows、macOS 和 Linux。该程序的功能列举如下:图层、块(分组)、35种CAD字体、40多种施工工具、20多种修改工具等等。许多用户都非常喜欢QCAD易于使用的界面和多功能性,给出了很高的评价。▲QCADImplicitCAD官网:implicitcad.org/ImplicitCAD网站表示:“ImplicitCAD项目致力于利用数学和计算机科学的力量来解决3D打印革命中的愚蠢设计问题”。ImplicitCAD是一款开源程序化CAD工具。这意味着ImplicitCAD使用了一种可以编译成3D对象的编程语言。程序化CAD的优点包括:对象的可重用性和抽象性;重复性任务的自动化;参数化设计以及软件开发(比如版本控制)的常用工具。▲ImplicitCAD▲ImplicitCADOpenSCAD官网:openscad.orgOpenSCAD是一款可以创建实体三维CAD模型的免费软件,可用于 Linux/UNIX、MS Windows和 MacOS X。它允许设计人员创建精确的3D模型和参数化设计,并且可以通过更改参数进行轻松调整。这些文档都是ASCII纯文本脚本,因此OpenSCAD更像是面向程序员的实体建模工具,通常被认为是设计开源硬件的入门级CAD工具,比如科研和教育科学工具。▲OpenSCAD四、电路仿真APP▲Droid PCB▲Circuit Wizard▲Bright Spark来自微信

几款免费好用的电路设计软件,你一定要试试! 果果小师弟嵌入式微处理器2022年09月16日12:01北京工程软件和在线资源往往比较昂贵,不过,对于专业人员、学生和爱好者来说是非常有益的。用户开展项目或者仅进行工程验证时,这些资源往往是必要的,但是相关成本却令许多人望而却步。今天给大家分享几款高质量的免费软件,相信你肯定喜欢!一、电路仿真PartSim网址:https://www.partsim.com/PartSim是一款基于浏览器的电路仿真器,用户可以通过该软件进行电路实验。该仿真器布局简单,从而确保易用性,同时提供完整的SPICE仿真引擎、基于Web的原理图捕获工具和图形示波器,可以监视电路的模拟/数字信号电平。该工具还包含Digi-Key BOM(物料清单),允许用户为设计组件分配零件号,然后找到分销商。▲PartSim▲PartSimEasyEDA网址:https://easyeda.com/EasyEDA旨在“通过为电子设计提供全面的数据和协作工具,帮助设计人员更快地将创意转化为制造原型”。EasyEDA提供免费的在线电路仿真、PCB设计和电子电路设计功能。人们可以访问大量的原理图元件库、PCB封装和包装、spice仿真、模型和子电路,从而节省设计时间。还可以邀请他人进行项目协作,并轻松地在团队中分享设计。标准版免费使用,并提供无限公共项目和2个私人项目。Autodesk Circuits网址:https://www.autodesk.com.cn/solutions/circuit-design-softwareAutodesk Circuits是用于电子设计和实验的一组工具。初学者可以通过Electronics Lab或Circuit Scribe开始简单的实验,而经验丰富的用户则可以直接跳至PCB设计。该软件提供大量的免费入门教程和项目教程,可以通过Electronics Lab学习。二、PCB设计DesignSpark PCB官网:https://www.rs-online.com/designspark/pcb-softwareDesignSpark PCB将自己称为世界上最易于使用的电子设计软件,专门用于快速原型设计,并且可以将你的电路想法更快地转化为可测试的电路板”。这个软件对原理图尺寸没有限制,所以用户在创建PCB设计时也没有限制。用户也可以导入和导出他们需要的任何格式的文件,并且能够以所需格式创建BOM(物料清单)。虽然该工具完全免费,但是要注意重要的一点,即用户必须在其网站上注册才能解锁程序,并且在开始工作之前必须确认所显示的广告。▲DesignSpark PCB▲DesignSpark PCB▲DesignSpark PCB▲DesignSparkPCBKiCadEDA网址:https://www.kicad.org/KiCad是一款跨平台的开源电子设计自动化套件。该套件由三个不同的工具组成:Eeschema(原理图捕捉)、PcbNEW(PCB布局)和3D Viewer(通过3D方式查看电路板设计)。其中3D Viewer是一个独特的工具,可以旋转和平移你的电路板,从而查看2D图中无法看到的细节。▲KiCad▲KiCad▲KiCad三、CAD建模FreeCAD网址:freecadweb.org/FreeCAD是一款多平台开源参数化3D建模工具,旨在帮助用户将设计项目变为现实。这是一款通用多功能工具,适合不同级别的用户。想要涉及3D打印的初学者、教育工作者或经验丰富的CAD用户都可以使用FreeCAD。程序员还可以利用Python“扩展FreeCAD的功能、用脚本实现自动化、构建自己的模块,甚至将FreeCAD嵌入到自己的应用程序中。”▲FreeCAD▲FreeCAD▲FreeCADQCAD网址:qcad.org/en/QCAD是一款免费的开源2D CAD应用程序。QCAD 是一个免费的开源应用程序,用于二维 (2D) 计算机辅助绘图 (CAD)。使用 QCAD,您可以创建技术图纸,例如建筑平面图、室内设计、机械零件或示意图和图表。QCAD 适用于 Windows、macOS 和 Linux。该程序的功能列举如下:图层、块(分组)、35种CAD字体、40多种施工工具、20多种修改工具等等。许多用户都非常喜欢QCAD易于使用的界面和多功能性,给出了很高的评价。▲QCADImplicitCAD官网:implicitcad.org/ImplicitCAD网站表示:“ImplicitCAD项目致力于利用数学和计算机科学的力量来解决3D打印革命中的愚蠢设计问题”。ImplicitCAD是一款开源程序化CAD工具。这意味着ImplicitCAD使用了一种可以编译成3D对象的编程语言。程序化CAD的优点包括:对象的可重用性和抽象性;重复性任务的自动化;参数化设计以及软件开发(比如版本控制)的常用工具。▲ImplicitCAD▲ImplicitCADOpenSCAD官网:openscad.orgOpenSCAD是一款可以创建实体三维CAD模型的免费软件,可用于 Linux/UNIX、MS Windows和 MacOS X。它允许设计人员创建精确的3D模型和参数化设计,并且可以通过更改参数进行轻松调整。这些文档都是ASCII纯文本脚本,因此OpenSCAD更像是面向程序员的实体建模工具,通常被认为是设计开源硬件的入门级CAD工具,比如科研和教育科学工具。▲OpenSCAD四、电路仿真APP▲Droid PCB▲Circuit Wizard▲Bright Spark来自微信 -

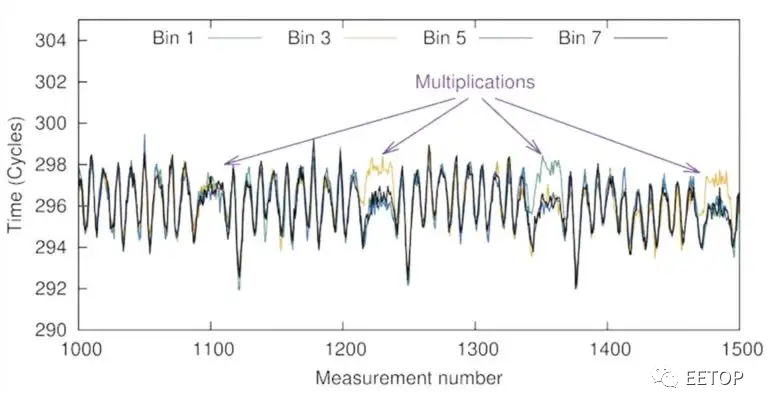

SoC硬漏洞 EET0P编译EET0P2021年08月06日04:32来源:EETOP编译整理自semiwiki 我经常看到有关计算机系统被黑客入侵、某某CPU被爆出漏洞等的文章。那么有哪些最佳实践可以让您的新的或现有的电子系统更能抵御攻击,并且不易受到攻击?Gajinder Panesar 和 Tim Ramsdale 分别是来自 Siemens EDA 和 Agile Analog 的两位专家,他们联手撰写了一份 15 页的白皮书,“ SoC 漏洞和模拟威胁的演进格局” 。接下来我们分享一些从阅读本文中学到的要点。(关注EETOP公众号,后台输入关键词:漏洞 ,获取白皮书)漏洞 一个安全前提是仅依靠软件更新来修补漏洞是不够的,因此应考虑将安全性作为硬件设计的一部分。甚至还有一个名为OpenTitan的开源项目,可帮助您为硅信任根(RoT) 芯片构建透明、高质量的参考设计和集成指南。使用基于硬件的 RoT,只能运行与已知签名进行比较的固件,从而阻止加载任何被黑固件的尝试。 黑客们变得越来越有创造力和足智多能,通过硬件测量来检查RSA算法中的密钥,,并注意到操作执行方式的微小变化,也就是侧通道攻击。下面显示的是紫色箭头的四个乘法部分,那么负尖峰是算法中的平方和模块化还原的一部分。侧道攻击 可以通过检查以下几件事来揭示安全线索:缓存活动执行管道电磁 (EM)值电压变化电流变化 侧道攻击的另一个例子是黑客试图猜测其中一个关键字节,并且在下图的350 附近他们找到了一个正确的关键字节。攻击输出与子密钥猜测的样本数 黑客攻击的目标包括 5G 基础设施、边缘服务器、物联网设备、云计算、自动驾驶汽车、工业机器人。黑客正在使用统计方法来衡量电子设备,为安全漏洞提供线索。一种对策是让硬件设计团队添加随机电噪声。正如德国安全公司LevelDown所记录的那样,黑客使用的另一种技术是在特定时间点故意干扰电源,然后将存储的位翻转到不安全状态。甚至一些较旧的处理器也存在黑客使用非法操作码的漏洞,从而使处理器处于易受攻击的状态。温度是另一种技术,攻击者可以在高于或低于指定温度的温度下运行 SoC,以改变内部状态,甚至从物理不可克隆功能 (PUF) 中提取私钥。攻击者可能利用电源轨的电压变化,以减慢或加快逻辑,导致内部比特翻转,并达到非法状态。如果黑客可以物理访问您的电子系统,他们通过改变占空比或引入毛刺直接控制时钟输入将改变内部逻辑。 ChipWhisperer是一家拥有开源系统的公司,使用侧信道功率分析和故障注入来暴露嵌入式系统的弱点。使用电磁(EM)辐射进行故障注入是ChipShouter公司使用的一种技术,但它们必须与内部时钟边缘精确定时,以创造一个可重复的故障。即使是在去掉盖子的IC封装上使用激光,也能迫使一个SoC出现内部错误。 漏洞对策 时钟毛刺:内部生成的比较源。 电源毛刺:断电检测器 温度攻击:温度传感器 在白皮书中,他们提供了一种名为Tessent Embedded Analytics的产品,它将硬件监视器嵌入到您的 SoC 中,然后与基于消息的架构进行通信。添加来自Agile Analog 的硬件安全 IP 可以检查时钟、电压和温度:来自 Agile Analog 的监视器这些监视器可以感知漏洞利用,然后嵌入式分析可以报告并决定适当的安全响应。嵌入式分析和安全 IP 的组合如图所示:嵌入式分析和安全 IP总结SoC 设计的强大功能和优势正受到黑客的攻击,因此设计社区有责任采取主动措施来加强其新产品的安全级别。西门子 EDA 和 Agile Analog 创建了一个嵌入式数字和模拟硬件框架,用于检测网络威胁,并实时采取适当行动。来自微信

SoC硬漏洞 EET0P编译EET0P2021年08月06日04:32来源:EETOP编译整理自semiwiki 我经常看到有关计算机系统被黑客入侵、某某CPU被爆出漏洞等的文章。那么有哪些最佳实践可以让您的新的或现有的电子系统更能抵御攻击,并且不易受到攻击?Gajinder Panesar 和 Tim Ramsdale 分别是来自 Siemens EDA 和 Agile Analog 的两位专家,他们联手撰写了一份 15 页的白皮书,“ SoC 漏洞和模拟威胁的演进格局” 。接下来我们分享一些从阅读本文中学到的要点。(关注EETOP公众号,后台输入关键词:漏洞 ,获取白皮书)漏洞 一个安全前提是仅依靠软件更新来修补漏洞是不够的,因此应考虑将安全性作为硬件设计的一部分。甚至还有一个名为OpenTitan的开源项目,可帮助您为硅信任根(RoT) 芯片构建透明、高质量的参考设计和集成指南。使用基于硬件的 RoT,只能运行与已知签名进行比较的固件,从而阻止加载任何被黑固件的尝试。 黑客们变得越来越有创造力和足智多能,通过硬件测量来检查RSA算法中的密钥,,并注意到操作执行方式的微小变化,也就是侧通道攻击。下面显示的是紫色箭头的四个乘法部分,那么负尖峰是算法中的平方和模块化还原的一部分。侧道攻击 可以通过检查以下几件事来揭示安全线索:缓存活动执行管道电磁 (EM)值电压变化电流变化 侧道攻击的另一个例子是黑客试图猜测其中一个关键字节,并且在下图的350 附近他们找到了一个正确的关键字节。攻击输出与子密钥猜测的样本数 黑客攻击的目标包括 5G 基础设施、边缘服务器、物联网设备、云计算、自动驾驶汽车、工业机器人。黑客正在使用统计方法来衡量电子设备,为安全漏洞提供线索。一种对策是让硬件设计团队添加随机电噪声。正如德国安全公司LevelDown所记录的那样,黑客使用的另一种技术是在特定时间点故意干扰电源,然后将存储的位翻转到不安全状态。甚至一些较旧的处理器也存在黑客使用非法操作码的漏洞,从而使处理器处于易受攻击的状态。温度是另一种技术,攻击者可以在高于或低于指定温度的温度下运行 SoC,以改变内部状态,甚至从物理不可克隆功能 (PUF) 中提取私钥。攻击者可能利用电源轨的电压变化,以减慢或加快逻辑,导致内部比特翻转,并达到非法状态。如果黑客可以物理访问您的电子系统,他们通过改变占空比或引入毛刺直接控制时钟输入将改变内部逻辑。 ChipWhisperer是一家拥有开源系统的公司,使用侧信道功率分析和故障注入来暴露嵌入式系统的弱点。使用电磁(EM)辐射进行故障注入是ChipShouter公司使用的一种技术,但它们必须与内部时钟边缘精确定时,以创造一个可重复的故障。即使是在去掉盖子的IC封装上使用激光,也能迫使一个SoC出现内部错误。 漏洞对策 时钟毛刺:内部生成的比较源。 电源毛刺:断电检测器 温度攻击:温度传感器 在白皮书中,他们提供了一种名为Tessent Embedded Analytics的产品,它将硬件监视器嵌入到您的 SoC 中,然后与基于消息的架构进行通信。添加来自Agile Analog 的硬件安全 IP 可以检查时钟、电压和温度:来自 Agile Analog 的监视器这些监视器可以感知漏洞利用,然后嵌入式分析可以报告并决定适当的安全响应。嵌入式分析和安全 IP 的组合如图所示:嵌入式分析和安全 IP总结SoC 设计的强大功能和优势正受到黑客的攻击,因此设计社区有责任采取主动措施来加强其新产品的安全级别。西门子 EDA 和 Agile Analog 创建了一个嵌入式数字和模拟硬件框架,用于检测网络威胁,并实时采取适当行动。来自微信 -

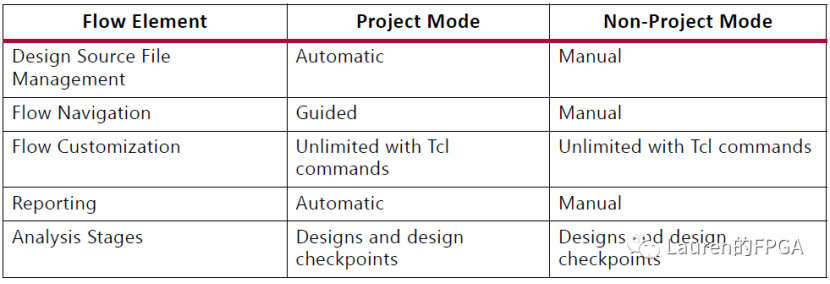

用Tcl实现Vivado设计全流程 Vivado有两种工作模式:project模式和non-project模式。这两种模式都可以借助VivadoIDE或Tcl命令来运行。相比之下,VivadoIDE给project模式提供了更多的好处,而Tcl命令使得non-project模式运行起来更简单。在project模式下,Vivado会自动管理整个设计流程和文件数据。最直接的体现是在Vivado左侧导航Flow Navigator下会显示所有流程,从设计输入到最终生成bit文件。同时,Vivado会自动创建相应的文件目录,生成相应的文件例如dcp以及相应的报告。Non-project模式是一种内存编译流程。用户可以从指定位置读取文件到内存中,然后进行编译。可以逐步执行每个步骤如综合、布局、布线等,可以根据需求设定编译参数。这一切都可以通过Tcl命令完成。显然,non-project模式下,用户可以通过Tcl命令管理设计文件和设计流程,体现了该模式的主要优势即用户对设计流程有完全的掌控力。Project模式和non-project模式的主要区别如下图所示。不难看出,project模式下更多的管理、操作都是“自动”完成的;而non-project模式下,则是“手工”完成的。从Tcl命令的角度而言,project和non-project模式也是不同的,如下图所示。Project模式下用到的Tcl命令是一种打包的命令,例如添加设计文件需用add_files,文件可以是HDL(包括VHDL,Verilog或SystemVerilog),可以是约束文件(包括.xdc或.tcl),可以是网表文件(可以是dcp,ngc或edif)等。Implementation时,命令launch_runs就可以按照指定的策略完成所有的步骤,包括生成相应的DCP。Non-project模式下用到的Tcl命令是分立的,例如,读入设计文件,如果是VHDL,需要用到read_vhdl;如果是Verilog,需要用到read_verilog,如果是.xdc,需要用到read_xdc;如果是DCP,需要用到read_checkpoint;如果是EDIF,需要用到read_edif。而在implementation时,需要分别用到opt_design、place_design、phys_opt_design和route_design等。因为Tcl命令使得non-project模式更能简单地运行,这里我们将介绍如何通过Tcl命令在non-project模式下完成所有步骤。有道云笔记2021-11-04 16:41:15

用Tcl实现Vivado设计全流程 Vivado有两种工作模式:project模式和non-project模式。这两种模式都可以借助VivadoIDE或Tcl命令来运行。相比之下,VivadoIDE给project模式提供了更多的好处,而Tcl命令使得non-project模式运行起来更简单。在project模式下,Vivado会自动管理整个设计流程和文件数据。最直接的体现是在Vivado左侧导航Flow Navigator下会显示所有流程,从设计输入到最终生成bit文件。同时,Vivado会自动创建相应的文件目录,生成相应的文件例如dcp以及相应的报告。Non-project模式是一种内存编译流程。用户可以从指定位置读取文件到内存中,然后进行编译。可以逐步执行每个步骤如综合、布局、布线等,可以根据需求设定编译参数。这一切都可以通过Tcl命令完成。显然,non-project模式下,用户可以通过Tcl命令管理设计文件和设计流程,体现了该模式的主要优势即用户对设计流程有完全的掌控力。Project模式和non-project模式的主要区别如下图所示。不难看出,project模式下更多的管理、操作都是“自动”完成的;而non-project模式下,则是“手工”完成的。从Tcl命令的角度而言,project和non-project模式也是不同的,如下图所示。Project模式下用到的Tcl命令是一种打包的命令,例如添加设计文件需用add_files,文件可以是HDL(包括VHDL,Verilog或SystemVerilog),可以是约束文件(包括.xdc或.tcl),可以是网表文件(可以是dcp,ngc或edif)等。Implementation时,命令launch_runs就可以按照指定的策略完成所有的步骤,包括生成相应的DCP。Non-project模式下用到的Tcl命令是分立的,例如,读入设计文件,如果是VHDL,需要用到read_vhdl;如果是Verilog,需要用到read_verilog,如果是.xdc,需要用到read_xdc;如果是DCP,需要用到read_checkpoint;如果是EDIF,需要用到read_edif。而在implementation时,需要分别用到opt_design、place_design、phys_opt_design和route_design等。因为Tcl命令使得non-project模式更能简单地运行,这里我们将介绍如何通过Tcl命令在non-project模式下完成所有步骤。有道云笔记2021-11-04 16:41:15 -

KEIL5 仿真 —— 示波器显示(2021-11-18) 记录一下如何使用 KEIL5 的示波器查看变量波形。这里先列出我参考的资料:你知道 KEIL 自带示波器吗?STM32:keil的软件逻辑分析仪( logic analyzer)使用调节项目的 Xtal 为 8KHzDebug 出选择 "Use Simulator","Dialog DLL" 和 "Parameter" 也需要更改,软件仿真填入 "DARMSTM.DLL" ,参数为 "-pSTM32F103VE",这里是我的STM32芯片型号。硬件仿真填入 "TARMSTM.DLL" 。然后点击仿真按钮开始仿真。打开逻辑分析仪窗口。点击 View 菜单,选择 "Symbols Window" 选项,在弹出的窗口里 "Special Function Register" 里找到查看波形的引脚。这里比如 GPIOB_IDR,按住后将其拖入逻辑分析仪窗口。点击 "Setup",将 "Display Type" 选为 "Bit",且用 "And Mask" 和 "Shift Right" 来过滤掉不需要显示的位。关闭,全速运行,即可看见指定引脚的波形。有道云笔记2021-11-18

KEIL5 仿真 —— 示波器显示(2021-11-18) 记录一下如何使用 KEIL5 的示波器查看变量波形。这里先列出我参考的资料:你知道 KEIL 自带示波器吗?STM32:keil的软件逻辑分析仪( logic analyzer)使用调节项目的 Xtal 为 8KHzDebug 出选择 "Use Simulator","Dialog DLL" 和 "Parameter" 也需要更改,软件仿真填入 "DARMSTM.DLL" ,参数为 "-pSTM32F103VE",这里是我的STM32芯片型号。硬件仿真填入 "TARMSTM.DLL" 。然后点击仿真按钮开始仿真。打开逻辑分析仪窗口。点击 View 菜单,选择 "Symbols Window" 选项,在弹出的窗口里 "Special Function Register" 里找到查看波形的引脚。这里比如 GPIOB_IDR,按住后将其拖入逻辑分析仪窗口。点击 "Setup",将 "Display Type" 选为 "Bit",且用 "And Mask" 和 "Shift Right" 来过滤掉不需要显示的位。关闭,全速运行,即可看见指定引脚的波形。有道云笔记2021-11-18 -

![Vivado综合时出现[Synth 8-91] ambiguous clock in event control(2021-11-24 )]((http://www.bennyhe.cn/usr/uploads/2025/06/1063405745.jpg) Vivado综合时出现[Synth 8-91] ambiguous clock in event control(2021-11-24 ) 在网上找了一波,改了一波,发现并没有消掉错误,头比较大,最终还是成功解决掉了。产生这种错误有两种情况第一种情况:定位在这个always块,我们通常习惯边缘触发,时钟上升沿和复位下降沿写到一起,但是,在always块里面并没有初始化的一些变量,也就是我们并没有用到rst_n,所以综合的时候就会报出上面的错误,将触发模式更改为always@(posedge clk)即可。第二种情况就是赋值冲突:同一个always块里可以允许两个if并行处理,但是这两个if所处理的内容不能有所交集,不然会产生赋值冲突,硬件电路不知道先处理哪个if的操作,也不能构建硬件电路,举个例子,如下图:第一个if else模块和第二个if else模块都对cnt进行了赋值,这是不允许的,综合是不能通过的,也会报相应错误。有道云笔记2021-11-24 18:24:11

Vivado综合时出现[Synth 8-91] ambiguous clock in event control(2021-11-24 ) 在网上找了一波,改了一波,发现并没有消掉错误,头比较大,最终还是成功解决掉了。产生这种错误有两种情况第一种情况:定位在这个always块,我们通常习惯边缘触发,时钟上升沿和复位下降沿写到一起,但是,在always块里面并没有初始化的一些变量,也就是我们并没有用到rst_n,所以综合的时候就会报出上面的错误,将触发模式更改为always@(posedge clk)即可。第二种情况就是赋值冲突:同一个always块里可以允许两个if并行处理,但是这两个if所处理的内容不能有所交集,不然会产生赋值冲突,硬件电路不知道先处理哪个if的操作,也不能构建硬件电路,举个例子,如下图:第一个if else模块和第二个if else模块都对cnt进行了赋值,这是不允许的,综合是不能通过的,也会报相应错误。有道云笔记2021-11-24 18:24:11

![Vivado综合时出现[Synth 8-91] ambiguous clock in event control(2021-11-24 )](http://www.bennyhe.cn/usr/uploads/2025/07/3844719267.png)