搜索到

18

篇与

的结果

-

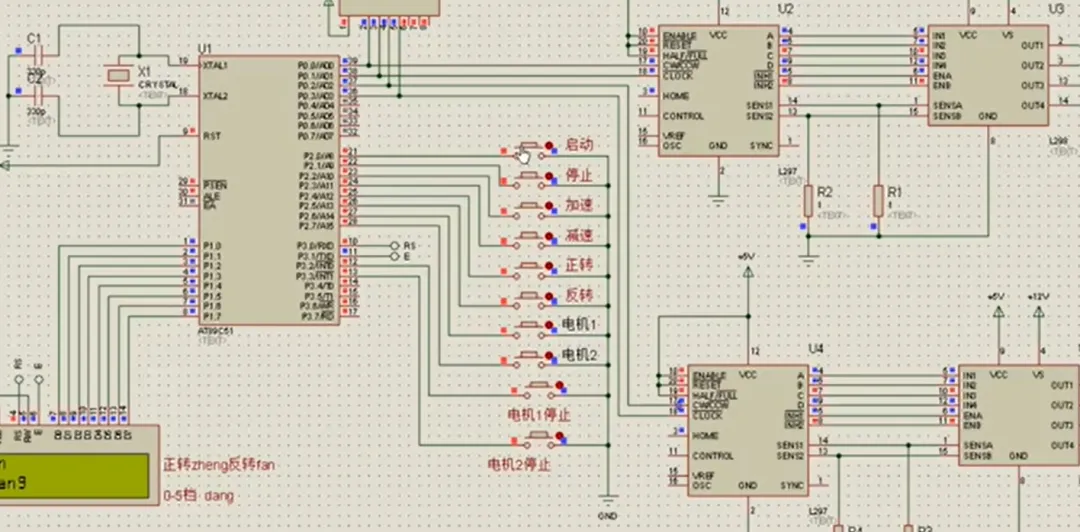

分享几款主流的EDA仿真软件(模拟电路) 摘要:电路仿真,顾名思义就是设计好的电路图通过仿真软件进行实时模拟,模拟出实际功能,然后通过其分析改进,从而实现电路的优化设计;是EDA(电子设计自动化)的一部分。市面上有各种类型的仿真器,本文对其中几款十分具有代表性的电路仿真软件进行了简要介绍,希望能对大家有所帮助。1、proteusProteus是英国著名的EDA工具,从原理图布图、代码调试到单片机与外围电路协同仿真,一键切换到:PCB设计,真正实现了从概念到产品的完整设计,是世界上唯一将电路仿真软件、PCB设计软件和虚拟模型仿真软件三合一的设计平台,其处理器模型支持8051、HC11、PIC10/12/16/18/24/30/DSPIC33、AVR、ARM、8086和MSP430等;2010年又增加了Cortex和DSP系列处理器,并持续增加其他系列处理器模型。在编译方面,它也支持IAR、Keil和Matlab等多种编译器。Proteus是一个巨大的教学资源,在模拟电子、数字电路、单片机与嵌入式教学等实践中被广泛应用。软件下载地址:https://www.labcenter.com/downloads/网盘下载地址:https://pan.baidu.com/s/1HwMD3eXIyNx_OAuu4QJGwQ提取码:inmu2、LTspiceLTspice是一款高性能SPICE仿真软件、原理图采集和波形查看器,集成增强功能和模型,简化了模拟电路的仿真。是半导体制造商Analog Devices出品的基于Spice的软件,功能同样强大,使用非常广泛。LTspice是一款高性能SPICE仿真软件、原理图采集和波形查看器,集成增强功能和模型,简化了模拟电路的仿真。在网上搜索“LTspice simulator”就能找到软件的主页,主页提供了软件的不同版本,可以按照自己的操作系统选择适合的版本下载并安装,软件大小不到60M,安装非常简单。下图给出的是软件打开后的演示界面。软件下载地址:https://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html3、Tina-TI德州仪器公司(TI)与DesignSoft公司联合为客户提供了一个强大的电路仿真工具TINA-TI。TINA-TI适用于对模拟电路和开关式电源(SMPS)电路的仿真,是进行电路开发与测试的理想选择。TINA基于SPICE引擎,是一款功能强大而易于使用的电路仿真工具;而TINA-TI 则是完整功能版本的TINA,并加载了TI公司的宏模型以及无源和有源器件模型。TI之所以选择TINA仿真软件而不是其它的基于SPICE技术的仿真器,是因为它同时具有强大的分析能力和简单直观的图形界面,并且易于使用。TINA-TI 提供了多种分析功能,包括SPICE的所有传统直流、交流、瞬态、频域、噪声分析等功能。虚拟仪器非常直观且功能丰富,允许用户选择输入波形、探针电路节点电压和波形。TINA的原理图捕捉非常直观,使用户真正能够“快速入门”。另外TINA具有广泛的后处理功能,允许用户设置输出结果的格式。软件下载地址:https://www.ti.com.cn/tool/cn/TINA-TI网盘下载地址:https://pan.baidu.com/s/1-QAWMDpRVVodTpksfRk3jw 提取码:6u8t4、MultismMultisim(旧名Electronics Workbench)是一款著名的电子设计自动化软件,与NI Ultiboard同属美国国家仪器公司的电路设计软件套件。是入选伯克利加大SPICE项目中为数不多的几款软件之一。Multisim在学术界以及产业界被广泛地应用于电路教学、电路图设计以及SPICE模拟。工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。Multisim提炼了SPICE仿真的复杂内容,这样工程师无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。通过Multisim和虚拟仪器技术,PCB设计工程师和电子学教育工作者可以完成从理论到原理图捕获与仿真再到原型设计和测试这样一个完整的综合设计流程。其前身是加拿大EWB仿真软件,被美国NI公司收购之后,其性能得到了极大的提升。最大的改变就是:Multisim 9与LABⅥEW 8的完美结合。网盘下载地址:https://pan.baidu.com/s/1iRz-ZcGbt54GFM8Q69iiOg提取码:2x4c5、Scratch最后再给大家介绍一款我经常使用的轻量级在线电路仿真工具,其特点是轻量化,上手更容易。贴几个动态GIF,让大家看看效果:1、施密特触发器1)、施密特触发器2)、Flash型ADC3)、差分放大器4)、高通滤波器5)、诺顿定理6)、运放741内部工作机理软件地址:http://scratch.trtos.com/circuitjs.html来自微信

分享几款主流的EDA仿真软件(模拟电路) 摘要:电路仿真,顾名思义就是设计好的电路图通过仿真软件进行实时模拟,模拟出实际功能,然后通过其分析改进,从而实现电路的优化设计;是EDA(电子设计自动化)的一部分。市面上有各种类型的仿真器,本文对其中几款十分具有代表性的电路仿真软件进行了简要介绍,希望能对大家有所帮助。1、proteusProteus是英国著名的EDA工具,从原理图布图、代码调试到单片机与外围电路协同仿真,一键切换到:PCB设计,真正实现了从概念到产品的完整设计,是世界上唯一将电路仿真软件、PCB设计软件和虚拟模型仿真软件三合一的设计平台,其处理器模型支持8051、HC11、PIC10/12/16/18/24/30/DSPIC33、AVR、ARM、8086和MSP430等;2010年又增加了Cortex和DSP系列处理器,并持续增加其他系列处理器模型。在编译方面,它也支持IAR、Keil和Matlab等多种编译器。Proteus是一个巨大的教学资源,在模拟电子、数字电路、单片机与嵌入式教学等实践中被广泛应用。软件下载地址:https://www.labcenter.com/downloads/网盘下载地址:https://pan.baidu.com/s/1HwMD3eXIyNx_OAuu4QJGwQ提取码:inmu2、LTspiceLTspice是一款高性能SPICE仿真软件、原理图采集和波形查看器,集成增强功能和模型,简化了模拟电路的仿真。是半导体制造商Analog Devices出品的基于Spice的软件,功能同样强大,使用非常广泛。LTspice是一款高性能SPICE仿真软件、原理图采集和波形查看器,集成增强功能和模型,简化了模拟电路的仿真。在网上搜索“LTspice simulator”就能找到软件的主页,主页提供了软件的不同版本,可以按照自己的操作系统选择适合的版本下载并安装,软件大小不到60M,安装非常简单。下图给出的是软件打开后的演示界面。软件下载地址:https://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html3、Tina-TI德州仪器公司(TI)与DesignSoft公司联合为客户提供了一个强大的电路仿真工具TINA-TI。TINA-TI适用于对模拟电路和开关式电源(SMPS)电路的仿真,是进行电路开发与测试的理想选择。TINA基于SPICE引擎,是一款功能强大而易于使用的电路仿真工具;而TINA-TI 则是完整功能版本的TINA,并加载了TI公司的宏模型以及无源和有源器件模型。TI之所以选择TINA仿真软件而不是其它的基于SPICE技术的仿真器,是因为它同时具有强大的分析能力和简单直观的图形界面,并且易于使用。TINA-TI 提供了多种分析功能,包括SPICE的所有传统直流、交流、瞬态、频域、噪声分析等功能。虚拟仪器非常直观且功能丰富,允许用户选择输入波形、探针电路节点电压和波形。TINA的原理图捕捉非常直观,使用户真正能够“快速入门”。另外TINA具有广泛的后处理功能,允许用户设置输出结果的格式。软件下载地址:https://www.ti.com.cn/tool/cn/TINA-TI网盘下载地址:https://pan.baidu.com/s/1-QAWMDpRVVodTpksfRk3jw 提取码:6u8t4、MultismMultisim(旧名Electronics Workbench)是一款著名的电子设计自动化软件,与NI Ultiboard同属美国国家仪器公司的电路设计软件套件。是入选伯克利加大SPICE项目中为数不多的几款软件之一。Multisim在学术界以及产业界被广泛地应用于电路教学、电路图设计以及SPICE模拟。工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。Multisim提炼了SPICE仿真的复杂内容,这样工程师无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。通过Multisim和虚拟仪器技术,PCB设计工程师和电子学教育工作者可以完成从理论到原理图捕获与仿真再到原型设计和测试这样一个完整的综合设计流程。其前身是加拿大EWB仿真软件,被美国NI公司收购之后,其性能得到了极大的提升。最大的改变就是:Multisim 9与LABⅥEW 8的完美结合。网盘下载地址:https://pan.baidu.com/s/1iRz-ZcGbt54GFM8Q69iiOg提取码:2x4c5、Scratch最后再给大家介绍一款我经常使用的轻量级在线电路仿真工具,其特点是轻量化,上手更容易。贴几个动态GIF,让大家看看效果:1、施密特触发器1)、施密特触发器2)、Flash型ADC3)、差分放大器4)、高通滤波器5)、诺顿定理6)、运放741内部工作机理软件地址:http://scratch.trtos.com/circuitjs.html来自微信 -

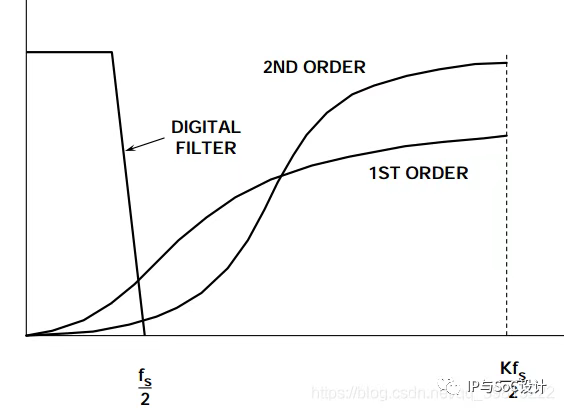

模拟IC设计:sigma delta ADC原理分析 KGback IP.与SoC设计2022年05月09日12:10江苏 一. ADC原理对于 Nyquist 和 Shannon 定理的检验将证明:ADC 采样频率的选择与最大输入信号频率对输入信号带宽的比率有很强的相关性。Nyquist准则(欠采样准则)如果要从相等时间间隔取得的采样点中,毫无失真地重建模拟信号波形,则采样频率必须大于或等于模拟信号中最高频率成份的两倍。因而对于一个最大信号频率为 fMAX的模拟信号 fa,其最小采样频率 fs,则有 fs ≥ 2 * fMAXNyquist频率:采样频率的一半,即 fs/2。从理论上来讲奈奎斯特频率正好大于输入信号的最大频率。Shannon定理一个带宽为fb的模拟信号,采样速率必须为 fs > 2fb,才能避免信息的损失。信号带宽可以从 DC 到 fb(基带采样),或从 f1 到f2,其中 fb = f2-f1(欠采样)。信号混叠如果不满足采样定理条件,采样后的信号的频率就会重叠。即被采样信号中高于采样频率一半(fs/2)的那部分频率成分将被重建成低于fs/2信号。这种频谱的重叠导致的失真称为混叠。(可借助车轮效应理解)(1)出现原因:若采样频率小于2倍的信号频率,即 fs < 2 * fa,那么,采样后的信号将存在混叠。理论上,如果信号中没有高于奈奎斯特频率的频率成分,那么则不存在混叠。(2)解决办法:a.提高采样频率 fs,一般实际应用中保证 fs 为 fMAX 的2.56~4倍。b.加一个低通滤波器:抗混叠滤波器理想状态下,该滤波器可使低于奈奎斯特频率的频率通过,移除高于奈奎斯特频率的频率成分性能指标(1)静态指标a.积分非线性(INL):输入一输出特性曲线与连接两端点的直线之间的最大偏差b.微分非线性(DNL):在输入轴上两个连续码转换点之间的差值与理想 1LSB 值的最大偏差c.失调:直线AB通过端点的垂直截距d.增益误差:直线AB的斜率与理想值1之间的偏差(2)动态指标a.信号与噪声失真比(SNDR):是当输入为正弦时,输出端信号功率与总噪声及谐波功率的比。b.动态范围:满量程正弦输入功率与肼限=0 dB时的正弦输入功率的比值c.总谐波失真:所有谐波能量(除去基波)之和除以基频的能量二. Σ-Δ 原理0.常用单级分类(1)根据modulator是否使用开关电容电路分a.连续时间模式(无开关电容):优点:功耗更小,无开关电容对时钟噪声不敏感,调制速度更快,常用于转换较高频率信号。缺点:要通过RC值来确定的积分系数,而不是像离散时间模式是用电容比值来确定的;对反馈回来的脉冲波形比较敏感,它会影响输入信号。b.离散时间模式则(有开关电容)与前者相反。(2)根据modulator阶数分所谓阶数指的是sigma—Delta调制器中积分器的个数。一般阶数越高幅频特性越好,低频段的衰减也越厉害,高频段的通过性越好所能达到的有效位数越大,但是延迟也会很大,也会减小输入信号的摆幅,另外,由于噪声在高频的幅值过大,会使整个系统的稳定性降低。(3)根据量化器的位数分可以分为一位调制器和多位调制器。使用多位量化器可以增加SNR,使系统容易稳定,产生较少的谐波分量,使降采样滤波器变得相对简单;但是多位量化器增加了ADC的复杂性,并且要求用于反馈的多位DAC有足够的精度来保证最后量化的精度。1.基本原理(图片来源于ANALOG DEVICES) (1)过采样指以高于信号带宽2倍或其最高频率对其采样的过程。K即为过采样率(OSR)。目的:a. 由于采用 Kfs 采样频率,均方根值为 q/√12 的量化噪声分布在 DC 到 Kfs/2 的带宽范围内,降低了某一频率下的噪声幅值,从而提高了信噪比,根据信噪比(SNR)和实际分辨率(ENOB)公式:ENOB=(SNR-1.76)/6.02 (SNR=6.02*N+1.76)可见提高了实际分辨率b.同时减轻了模拟抗混叠滤波器的要求(2)量化噪声整形(采样频率和量化值之间的关系,红线是实际电压值)离散化的阶梯型与红色的模拟信号相减的值即为量化噪声。实际上,阶梯型线条包围的面积和模拟信号包围的面积是相等的,即二者能量总量是相等的。量化噪声是消除不了的。根据频域线性模型y和x的关系,f越大,Q引起的噪声就越大,即类似高通滤波器(x部分则是低通滤波器)(3)数字抽取滤波通过数字滤波器将比较器输出的高频一位或多位量化值转换为频率较低的多位量化值。可理解为降采样滤波器可将n个输入信号加起来,然后除以n,这样获得输入的平均值。优点:当采样频率下降n倍时,fs/n及其谐波分量处的噪声被混叠到信号带内,其引入的噪声会比较小。(4)数据流的计算该部分举例分析:若调制器DAC的参考电压Vref为1V,现输入模拟电压值0.5V,则调制器输出为011101110111的序列,如图所示:3/4代表调制器分辨率为2,6/8代表分辨率为3则实际电压Vin=(3/4-2/4)(1-(-1))=0.5V, 即Vin=(weight(1)-1/2)Vref*2(5)频域线性模型输出值y和输入值x,以及量化噪声Q,信号频率f之间的关系2.ADC组成(图片来源于ANALOG DEVICES)(1)模拟部分:a.模拟抗混叠滤波器,b.ADC部分:一个比较器、一个基准电压源、一个开关以及一个或多个的积分器与模拟求和电路(2)数字部分:一个DSP(通常但不总是低通滤波器使用)三.设计流程1.数字抽取滤波器设计在设计数字滤波器时,滤波器的采样频率就是前端AD的采样频率。不同阶数的CIC滤波器的延迟问题:当数字滤波器处理来自Σ-Δ调制器的数据流的移动平均值时,存在一个相关的建立时间。该延迟对所有FIR滤波器是固定的,但对不同阶数的CIS滤波器,该延迟是不同的。通常用两项来描述该延迟:群延迟和建立时间。群延迟描述从输入端存在模拟信号到在数字输出端看到它的延迟时间。例如对于单音正弦波,群延迟就是从模拟输入端存在该正弦波电压峰值到该峰值出现在数字输出端的时间差。建立时间是指数字滤波器的全部均值时间。如果模拟输入端有一个阶跃,那么需要经过滤波器的完全建立时间, ADC的数据输出才与阶跃之前的输入无关。还可能存在其他延迟,如滤波器的计算时间等。本次设计的数字抽取滤波器为3阶的CIC滤波器,与一般的FIR滤波器相比,后者则需要大量的乘法器,而前者只需要加法器和延时,简化了运算,适合用于抽取前级和内插后级等告诉场合,但是也有明显不足:幅频特性无法像 FIR 那样灵活设计,因而有时在抽取的后级会用 FIR 来整形。因此该设计主要由级联积分梳状(CIC)抽取滤波器、CIC补偿滤波器和半带(HB)滤波器组成。cIc抽取滤波器作为数字抽取滤波器的第一级来达到降速作用;CIC补偿滤波器用来补偿通带的衰减;HB滤波器则用作抽取滤波器的阻带衰减及进一步降低采样频率。用FDAtool设计CIC decimator时,通带增益不是0dB,需要级联一个常数增益滤波器,CIC滤波器增益为D^Q,D是抽取因子,Q是级数,常数增益滤波器增益设置为1/(D^Q),就行,在脚本中输入 G=dfilt.scalar,G.Gain=1/(D^Q);然后从工作区引入滤波器,设置完参数和CIC级联。本文来源:https://blog.csdn.net/qq_39815222/article/details/103248394来自微信

模拟IC设计:sigma delta ADC原理分析 KGback IP.与SoC设计2022年05月09日12:10江苏 一. ADC原理对于 Nyquist 和 Shannon 定理的检验将证明:ADC 采样频率的选择与最大输入信号频率对输入信号带宽的比率有很强的相关性。Nyquist准则(欠采样准则)如果要从相等时间间隔取得的采样点中,毫无失真地重建模拟信号波形,则采样频率必须大于或等于模拟信号中最高频率成份的两倍。因而对于一个最大信号频率为 fMAX的模拟信号 fa,其最小采样频率 fs,则有 fs ≥ 2 * fMAXNyquist频率:采样频率的一半,即 fs/2。从理论上来讲奈奎斯特频率正好大于输入信号的最大频率。Shannon定理一个带宽为fb的模拟信号,采样速率必须为 fs > 2fb,才能避免信息的损失。信号带宽可以从 DC 到 fb(基带采样),或从 f1 到f2,其中 fb = f2-f1(欠采样)。信号混叠如果不满足采样定理条件,采样后的信号的频率就会重叠。即被采样信号中高于采样频率一半(fs/2)的那部分频率成分将被重建成低于fs/2信号。这种频谱的重叠导致的失真称为混叠。(可借助车轮效应理解)(1)出现原因:若采样频率小于2倍的信号频率,即 fs < 2 * fa,那么,采样后的信号将存在混叠。理论上,如果信号中没有高于奈奎斯特频率的频率成分,那么则不存在混叠。(2)解决办法:a.提高采样频率 fs,一般实际应用中保证 fs 为 fMAX 的2.56~4倍。b.加一个低通滤波器:抗混叠滤波器理想状态下,该滤波器可使低于奈奎斯特频率的频率通过,移除高于奈奎斯特频率的频率成分性能指标(1)静态指标a.积分非线性(INL):输入一输出特性曲线与连接两端点的直线之间的最大偏差b.微分非线性(DNL):在输入轴上两个连续码转换点之间的差值与理想 1LSB 值的最大偏差c.失调:直线AB通过端点的垂直截距d.增益误差:直线AB的斜率与理想值1之间的偏差(2)动态指标a.信号与噪声失真比(SNDR):是当输入为正弦时,输出端信号功率与总噪声及谐波功率的比。b.动态范围:满量程正弦输入功率与肼限=0 dB时的正弦输入功率的比值c.总谐波失真:所有谐波能量(除去基波)之和除以基频的能量二. Σ-Δ 原理0.常用单级分类(1)根据modulator是否使用开关电容电路分a.连续时间模式(无开关电容):优点:功耗更小,无开关电容对时钟噪声不敏感,调制速度更快,常用于转换较高频率信号。缺点:要通过RC值来确定的积分系数,而不是像离散时间模式是用电容比值来确定的;对反馈回来的脉冲波形比较敏感,它会影响输入信号。b.离散时间模式则(有开关电容)与前者相反。(2)根据modulator阶数分所谓阶数指的是sigma—Delta调制器中积分器的个数。一般阶数越高幅频特性越好,低频段的衰减也越厉害,高频段的通过性越好所能达到的有效位数越大,但是延迟也会很大,也会减小输入信号的摆幅,另外,由于噪声在高频的幅值过大,会使整个系统的稳定性降低。(3)根据量化器的位数分可以分为一位调制器和多位调制器。使用多位量化器可以增加SNR,使系统容易稳定,产生较少的谐波分量,使降采样滤波器变得相对简单;但是多位量化器增加了ADC的复杂性,并且要求用于反馈的多位DAC有足够的精度来保证最后量化的精度。1.基本原理(图片来源于ANALOG DEVICES) (1)过采样指以高于信号带宽2倍或其最高频率对其采样的过程。K即为过采样率(OSR)。目的:a. 由于采用 Kfs 采样频率,均方根值为 q/√12 的量化噪声分布在 DC 到 Kfs/2 的带宽范围内,降低了某一频率下的噪声幅值,从而提高了信噪比,根据信噪比(SNR)和实际分辨率(ENOB)公式:ENOB=(SNR-1.76)/6.02 (SNR=6.02*N+1.76)可见提高了实际分辨率b.同时减轻了模拟抗混叠滤波器的要求(2)量化噪声整形(采样频率和量化值之间的关系,红线是实际电压值)离散化的阶梯型与红色的模拟信号相减的值即为量化噪声。实际上,阶梯型线条包围的面积和模拟信号包围的面积是相等的,即二者能量总量是相等的。量化噪声是消除不了的。根据频域线性模型y和x的关系,f越大,Q引起的噪声就越大,即类似高通滤波器(x部分则是低通滤波器)(3)数字抽取滤波通过数字滤波器将比较器输出的高频一位或多位量化值转换为频率较低的多位量化值。可理解为降采样滤波器可将n个输入信号加起来,然后除以n,这样获得输入的平均值。优点:当采样频率下降n倍时,fs/n及其谐波分量处的噪声被混叠到信号带内,其引入的噪声会比较小。(4)数据流的计算该部分举例分析:若调制器DAC的参考电压Vref为1V,现输入模拟电压值0.5V,则调制器输出为011101110111的序列,如图所示:3/4代表调制器分辨率为2,6/8代表分辨率为3则实际电压Vin=(3/4-2/4)(1-(-1))=0.5V, 即Vin=(weight(1)-1/2)Vref*2(5)频域线性模型输出值y和输入值x,以及量化噪声Q,信号频率f之间的关系2.ADC组成(图片来源于ANALOG DEVICES)(1)模拟部分:a.模拟抗混叠滤波器,b.ADC部分:一个比较器、一个基准电压源、一个开关以及一个或多个的积分器与模拟求和电路(2)数字部分:一个DSP(通常但不总是低通滤波器使用)三.设计流程1.数字抽取滤波器设计在设计数字滤波器时,滤波器的采样频率就是前端AD的采样频率。不同阶数的CIC滤波器的延迟问题:当数字滤波器处理来自Σ-Δ调制器的数据流的移动平均值时,存在一个相关的建立时间。该延迟对所有FIR滤波器是固定的,但对不同阶数的CIS滤波器,该延迟是不同的。通常用两项来描述该延迟:群延迟和建立时间。群延迟描述从输入端存在模拟信号到在数字输出端看到它的延迟时间。例如对于单音正弦波,群延迟就是从模拟输入端存在该正弦波电压峰值到该峰值出现在数字输出端的时间差。建立时间是指数字滤波器的全部均值时间。如果模拟输入端有一个阶跃,那么需要经过滤波器的完全建立时间, ADC的数据输出才与阶跃之前的输入无关。还可能存在其他延迟,如滤波器的计算时间等。本次设计的数字抽取滤波器为3阶的CIC滤波器,与一般的FIR滤波器相比,后者则需要大量的乘法器,而前者只需要加法器和延时,简化了运算,适合用于抽取前级和内插后级等告诉场合,但是也有明显不足:幅频特性无法像 FIR 那样灵活设计,因而有时在抽取的后级会用 FIR 来整形。因此该设计主要由级联积分梳状(CIC)抽取滤波器、CIC补偿滤波器和半带(HB)滤波器组成。cIc抽取滤波器作为数字抽取滤波器的第一级来达到降速作用;CIC补偿滤波器用来补偿通带的衰减;HB滤波器则用作抽取滤波器的阻带衰减及进一步降低采样频率。用FDAtool设计CIC decimator时,通带增益不是0dB,需要级联一个常数增益滤波器,CIC滤波器增益为D^Q,D是抽取因子,Q是级数,常数增益滤波器增益设置为1/(D^Q),就行,在脚本中输入 G=dfilt.scalar,G.Gain=1/(D^Q);然后从工作区引入滤波器,设置完参数和CIC级联。本文来源:https://blog.csdn.net/qq_39815222/article/details/103248394来自微信 -

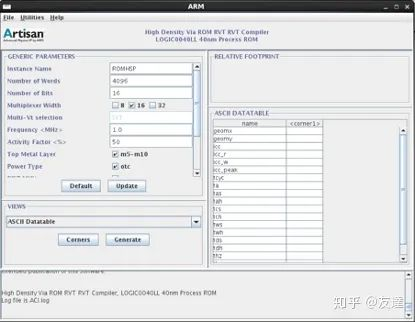

科普:Memory Compiler生成的Register file和SRAM有何区别? IP与S0C设计2021年09月03日04:01前两期,我们分别对OTP和MTP,RAM和ROM进行了比较。这一次,我们来谈谈Memory Compiler,以及通过它生成的Register file和SRAM。什么是Memory Compiler ?Memory Compiler,内存编译器。顾名思义,是用来生成不同容量memory的工具,输入参数,我们就可以得到生成的文件。生成的文件包括:前端设计verilog模型、逻辑综合的时序库、后端需要的电路网表和LEF/GDS版图文件、其他DFT验证相关的、datasheet手册等等。Memory Compiler由供应商提供,往往是不通用的,界面也不尽相同。同一个厂商的不同工艺下,Memory Compiler不同。相同工艺,不同厂商,Memory Compiler也不同。内存编译器通常是供应商的知识产权,其功能是根据客户的需求生成各种类型的memory。一般的Memory Compiler提供五个ram脚本(rf_sp,sram_sp,rf_tp,sram_dp,rom)。这意味着可以生成1 Port Register file、Single Port SRAM、2 Port Register file、Dual Port SRAM以及ROM。不同的厂商或许还拥有特殊工艺。一般来说,MC只生成常用的memory,特殊的往往需要定制或者组合。考虑到面积和性能,又可以划分为High Speed和High Density等等。图源知乎:SMIC 的Memory Compiler,由Artisan公司提供Memory Compiler使用介绍在使用Memory Compiler时,请务必确保你的RAM从头到位的规格与设定都相同,否则会造成一些不可避免的错误。首先在RTL代码阶段,要用到RAM就要用到verilog代码,此时不需要着急产生其他后阶段的必要数据,因为RTL代码阶段只需要行为级模型即可。当进入门级代码后,RAM compiler就要产生其他的相关数据了,同时要考虑RAM版图的位置与方向。由于重大的设计不会一蹴而就,所以有两个重点,第一个是每次使用RAM compiler时都一定要让它产生特性设置文档,避免忘记自己做过的设定。第二件事是对应的文件名要定义好,否则RAM的方向不同但是又用到了相同的文件名,就会把原始数据覆盖掉。RTL阶段在RTL阶段主要只是产生verilog行为级和设置文件。因为在RTL阶段不需要考虑RAM的位置信息。Memory Compiler提供多种选择,在这个阶段,选择生成RF或是SRAM,以及确定端口数量。如果容量比较大的话,相同设置下,单端口比双端口面积要小,速度也要快,功耗要低。综合与布局布线阶段为了避免重新启用Memory Compiler与以前设置有出入,所以最好一次性将Memory Compiler能够产生的相关数据一并输出。在这里,Memory Compiler还需要产生3种数据。 .LIB 该数据是RAM的时序信息文件 .VCLEF 布局布线工具需要使用的物理信息文件 .SPEC RAM的注释文件在布局布线前,需要考虑RAM的长与宽,估计它的位置与方向,尽量让功能想关的模块靠近一些。将产生的.LIB文件转换成.DB文件,就可以把Memory Compiler生成的RAM加入到代码中进行综合了。在综合工具的脚本中的serch_path下加入RAM的DB文件地址即可。以上为Memory Compiler大致的使用流程,不同的工具在细节上或许有所区别,但大体流程如此。苏州腾芯微电子的Memory Compiler界面接下来,我们来聊一聊,生成的memory——Register file和SRAM。Register file与SRAM的比较首先,厘清一下概念上的问题,Register file和很多的registers不是同一个概念。我们在IC设计里谈到register时,常常是指D触发器,而Register file是一种memory。那么,同为Memory Compiler生成,RF和SRAM有什么区别呢?在比较中,不同规格相比较显然不够客观,也不能让我们更清晰地认识到它们的差异。在比较前,我们需要先把端口的概念搞清楚: 1 port / single port:单端口,读写同端口,需要WE控制输入输出 2 port:双端口,读写分开,输入输出端口固定,可以不用WE控制 dual port:同样是双端口,但读写端口不固定,且都可读可写 RF 的端口示意图SRAM 的端口示意图所以我们应当把1P RF和SP SRAM,2P RF和DP SRAM比较,才有意义。1 Port Register file 和 Single Port SRAM同为单端口,从外部端口看,难以区分1P RF和SP SRAM的区别,但是我们可以从以下几个方面,来进行区分。首先我们以Memory Size:512*32的1P RF和SP SRAM为例。此为1P RF此为SP SRAM从datasheet直观上来看,SRAM比Register file多了OEN(输出使能)。除此之外,Register file和SRAM两者相比,SRAM的最大容量比RF要大。相同配置下,RF的面积更大,功耗更低。在mem比较小的情况下用RF划算,并且同样的mem,RF的长宽比会更小,方便后端floorplan。大容量的时候,SRAM的速度是有优势的。并且SRAM速度快,面积小。同样大小的RF,面积就很大了,速度也慢下来了。所以简单来说,小容量选RF,大容量选SRAM。2P Register file 和 Dual Port SRAM比起1P RF与SP SRAM的比较,2P RF与DP SRAM的差异较为直观。2P RF有一个输入数据总线,一个输出的数据总线。DP SRAM有两个数据输入总线,两个数据输出总线。换句话说,2P RF是一组信号,读写端口固定;而DP SRAM则有两组信号,读写不分开。且两组信号,每组都有自己的地址,输入数据总线,输出数据总线,时钟,读/写控制。这两组可以分别往存储单元写,或从存储单元读出。读可以一直读,写时数据可能存储单元数据更新,数据也可能输出端口。DP SRAM就好像2个SP SRAM共用存储单元。具体的应用,需要结合设计人员和项目自身的需求来选用。小容量,地址少的用RF。有两个外设要同时读写SRAM的,就要用DP SRAM。涉及到具体的选取,则需要由设计人员自己做判断了。以下为读写时序图:图源:数字IC自修室来自微信

科普:Memory Compiler生成的Register file和SRAM有何区别? IP与S0C设计2021年09月03日04:01前两期,我们分别对OTP和MTP,RAM和ROM进行了比较。这一次,我们来谈谈Memory Compiler,以及通过它生成的Register file和SRAM。什么是Memory Compiler ?Memory Compiler,内存编译器。顾名思义,是用来生成不同容量memory的工具,输入参数,我们就可以得到生成的文件。生成的文件包括:前端设计verilog模型、逻辑综合的时序库、后端需要的电路网表和LEF/GDS版图文件、其他DFT验证相关的、datasheet手册等等。Memory Compiler由供应商提供,往往是不通用的,界面也不尽相同。同一个厂商的不同工艺下,Memory Compiler不同。相同工艺,不同厂商,Memory Compiler也不同。内存编译器通常是供应商的知识产权,其功能是根据客户的需求生成各种类型的memory。一般的Memory Compiler提供五个ram脚本(rf_sp,sram_sp,rf_tp,sram_dp,rom)。这意味着可以生成1 Port Register file、Single Port SRAM、2 Port Register file、Dual Port SRAM以及ROM。不同的厂商或许还拥有特殊工艺。一般来说,MC只生成常用的memory,特殊的往往需要定制或者组合。考虑到面积和性能,又可以划分为High Speed和High Density等等。图源知乎:SMIC 的Memory Compiler,由Artisan公司提供Memory Compiler使用介绍在使用Memory Compiler时,请务必确保你的RAM从头到位的规格与设定都相同,否则会造成一些不可避免的错误。首先在RTL代码阶段,要用到RAM就要用到verilog代码,此时不需要着急产生其他后阶段的必要数据,因为RTL代码阶段只需要行为级模型即可。当进入门级代码后,RAM compiler就要产生其他的相关数据了,同时要考虑RAM版图的位置与方向。由于重大的设计不会一蹴而就,所以有两个重点,第一个是每次使用RAM compiler时都一定要让它产生特性设置文档,避免忘记自己做过的设定。第二件事是对应的文件名要定义好,否则RAM的方向不同但是又用到了相同的文件名,就会把原始数据覆盖掉。RTL阶段在RTL阶段主要只是产生verilog行为级和设置文件。因为在RTL阶段不需要考虑RAM的位置信息。Memory Compiler提供多种选择,在这个阶段,选择生成RF或是SRAM,以及确定端口数量。如果容量比较大的话,相同设置下,单端口比双端口面积要小,速度也要快,功耗要低。综合与布局布线阶段为了避免重新启用Memory Compiler与以前设置有出入,所以最好一次性将Memory Compiler能够产生的相关数据一并输出。在这里,Memory Compiler还需要产生3种数据。 .LIB 该数据是RAM的时序信息文件 .VCLEF 布局布线工具需要使用的物理信息文件 .SPEC RAM的注释文件在布局布线前,需要考虑RAM的长与宽,估计它的位置与方向,尽量让功能想关的模块靠近一些。将产生的.LIB文件转换成.DB文件,就可以把Memory Compiler生成的RAM加入到代码中进行综合了。在综合工具的脚本中的serch_path下加入RAM的DB文件地址即可。以上为Memory Compiler大致的使用流程,不同的工具在细节上或许有所区别,但大体流程如此。苏州腾芯微电子的Memory Compiler界面接下来,我们来聊一聊,生成的memory——Register file和SRAM。Register file与SRAM的比较首先,厘清一下概念上的问题,Register file和很多的registers不是同一个概念。我们在IC设计里谈到register时,常常是指D触发器,而Register file是一种memory。那么,同为Memory Compiler生成,RF和SRAM有什么区别呢?在比较中,不同规格相比较显然不够客观,也不能让我们更清晰地认识到它们的差异。在比较前,我们需要先把端口的概念搞清楚: 1 port / single port:单端口,读写同端口,需要WE控制输入输出 2 port:双端口,读写分开,输入输出端口固定,可以不用WE控制 dual port:同样是双端口,但读写端口不固定,且都可读可写 RF 的端口示意图SRAM 的端口示意图所以我们应当把1P RF和SP SRAM,2P RF和DP SRAM比较,才有意义。1 Port Register file 和 Single Port SRAM同为单端口,从外部端口看,难以区分1P RF和SP SRAM的区别,但是我们可以从以下几个方面,来进行区分。首先我们以Memory Size:512*32的1P RF和SP SRAM为例。此为1P RF此为SP SRAM从datasheet直观上来看,SRAM比Register file多了OEN(输出使能)。除此之外,Register file和SRAM两者相比,SRAM的最大容量比RF要大。相同配置下,RF的面积更大,功耗更低。在mem比较小的情况下用RF划算,并且同样的mem,RF的长宽比会更小,方便后端floorplan。大容量的时候,SRAM的速度是有优势的。并且SRAM速度快,面积小。同样大小的RF,面积就很大了,速度也慢下来了。所以简单来说,小容量选RF,大容量选SRAM。2P Register file 和 Dual Port SRAM比起1P RF与SP SRAM的比较,2P RF与DP SRAM的差异较为直观。2P RF有一个输入数据总线,一个输出的数据总线。DP SRAM有两个数据输入总线,两个数据输出总线。换句话说,2P RF是一组信号,读写端口固定;而DP SRAM则有两组信号,读写不分开。且两组信号,每组都有自己的地址,输入数据总线,输出数据总线,时钟,读/写控制。这两组可以分别往存储单元写,或从存储单元读出。读可以一直读,写时数据可能存储单元数据更新,数据也可能输出端口。DP SRAM就好像2个SP SRAM共用存储单元。具体的应用,需要结合设计人员和项目自身的需求来选用。小容量,地址少的用RF。有两个外设要同时读写SRAM的,就要用DP SRAM。涉及到具体的选取,则需要由设计人员自己做判断了。以下为读写时序图:图源:数字IC自修室来自微信 -

-

ASIC设计学习总结(包括:工具及书籍文档推荐 、软件环境搭建、RTL设计、验证、工艺库说明、形式验证、综合等共12部分) 原创tfpwl——lj EET0P2019年02月07日09:57之前介绍过了了芯片设计全流程介绍(芯片设计全流程详解 包括:正向流程和反向流程)。由于当时的经验十分有限,所以对于正向设计,特别是对于从RTL级代码开始的设计介绍得不是很清楚。经过这一段时间的学习,对于从RTL级代码开始的Asic芯片设计有了更多的认识,现在总结一下,一方面给自己整理思路,另一方面也希望抛砖引玉,让大家各抒己见,分享一下各自的设计经验,促进我们的共同进步。笔者原本打算详细的介绍学习中的收获,将各类知识点写成文章,但经过反复考量之后,发现这种详细照搬别人知识的做法其实没什么意思。与其原封不动的转述别人书中的内容,不如直接提供参阅的书目,这样就免得在转述别人的知识的时候误解作者想要表达的真正意义。所以本系列的文章,笔者将个人学习的经验加以整合,将经验知识点罗列出来,并附加所参阅的书籍。另外涉及到实践操作过程的章节,将会把具体使用的工具罗列出来,并附上一些参考性的代码和脚本。本系列文章主要分为十二个部分,分别为:(一)工具及书籍文档推荐(二)软件环境搭建(三)RTL设计(四)验证(五)工艺库说明(六)形式验证(七)综合(八)可测性设计(九)低功耗设计(十)静态时序分析(十一)数模混合仿真(十二)可测性设计介绍这么多,不是显得个人有多少经验,其实本人也只是菜鸟,关注这么多内容,主要是为了让自己的知识储备更全面一下,这样考虑设计问题的时候遗漏的东西会更少一些。在本系列文章中,每个章节的详略是不同的,主要是跟个人工作经验有关,有介绍得简单的地方,麻烦大家帮忙补充。每个部分的内容基本采用“理论+工具+示例”的行文结构,有些EDA工具笔者没有使用过的就暂不能提供实例了。(一)工具及书籍文档一、前言对于RTL级的Asic设计所涉及到的软件是非常之多的,笔者也并没有每一个都使用过。二、工具介绍RTL代码规则检查工具:nlint,spyglass。这两个软件主要是用于检查代码的语法和语义错误的,并且比其他的工具能检测出更多的问题,比如说命名规格,时序风险,功耗等。详细介绍请参考软件的使用教程,nlint有Windows版和linux版,软件的linux版本和使用教程可以在eetop上搜索到。RTL代码仿真工具:这类仿真工具有较多的组合,比如说:qustasim/modelsim,NC_verilog+Verdi,VCS+DVE,VCS+Verdi等等。目前笔者使用的组合是VCS+Verdi。这两个软件是业内主流的仿真软件,还可以结合UVM库进行仿真,当然这是验证方法学的内容。综合工具:Design Complier。最常用的综合工具,没有之一,该软件主要是将RTL代码“翻译+优化+映射”成与工艺库对应的门级网表。并且还包含功耗分析软件Power Complier和边界扫描寄存器插入软件 BSD Complier。可测性设计:DFT Complier + TetraMAX。软件在DC之后使用,DFT Complier 用于将设计的内部寄存器替换成扫描寄存器并组成一条或多条扫描链,TetraMAX是用于自动生成测试向量的。形式验证工具:Formality、Conforml(candence出品)。等价性验证工具,主要是在DFT Complier插入扫描链之后进行验证,另外,在版图综合时钟树,插入BUFFER之后,也需要用该工具进行等效性验证。静态时序分析工具: Prime Time。业界最常用的时序分析工具之一,该软件包括功耗分析PTPX工具,功耗分析必备。cadence也有对应的时序分析工具——Encounter Timing System。自动布局布线工具(APR):ICC,Enconter。其中Encounter是Cadence公司的。数模混合仿真: nanosim + VCS,nanosim的升级版为XA。这是一篇有关于synopsysEDA工具软件的介绍,希望对于EDA软件的用途不清楚的伙伴有帮助。http://bbs.eetop.cn/thread-151171-1-1.html三、书籍推荐《Verilog HDL 硬件描述语言》《设计与验证Verilog HDL》《企业用verilog代码风格规范》《verilog语言编码风格》《verilogHDL代码风格规范》《Verilog HDL高级数字设计》《Soc设计方法与实现》《高级ASIC芯片综合》《华为Verilog典型电路设计》《数字IC系统设计》《数字集成电路--电路、系统与设计》《专用集成电路设计实用教程》《集成电路静态时序分析与建模》《CMOS集成电路后端设计与实战》《makefile教程》《鸟哥的私房菜》《SystemVerilog与功能验证》《UVM实战》《通信IC设计(上下册)》《数字图像处理与图像通信》《数字信号处理的FPGA实现中文版》各类Synopsy userguide,EETOP有16年版的。三、工艺库说明使用DC,PT,FM,ICC或者ENCOUNTER软件需要工艺库文件,主要包括数字逻辑单元文件,符号库,综合库,寄生电容参数库,版图文件LEF,milkway库等等。有关工艺库各文件夹的作用,笔者将会在将“工艺库说明”的章节进行详细介绍,如果有遗漏还请大家包涵。(二)环境搭建一、前言先介绍一下个人的使用环境。由于网络上已经存在很多安装教程,笔者就不再废话,直接给出他们的连接,并附带其他需要注意的关键点,如果有安装问题,请追问。Synopsys软件安装包下载地址在笔者前一篇文章“工具及书籍文档”,都是来自EETOP的大牛们提供的。在安装的过程中需要具备一些Linux系统的使用经验,不然会很难理解这些步骤是做什么的。个人的环境如下:1、vmware 12;2、RHEL6.5系统;3、synopsys软件,Lib Complier,VCS,Verdi,Desgin Complier,PrimeTime,Formality,ICC。一共7个软件,几乎都是15年版本的。二、步骤环境搭建需要准备以下三件事:1,vmware12虚拟机安装;安装教程如下。https://jingyan.baidu.com/article/215817f78879c21edb142379.html2, RHEL6.5操作系统安装,当然也可以使用CentOs6.5,安装教程如下。http://www.linuxidc.com/Linux/2016-05/131701.htm ——》RHEL6.5https://www.kafan.cn/edu/488101.html ——》Centos6.5a、安装vmware tools。在虚拟机中把系统安装好了之后,需要安装vmware tools,安装教程如下,http://www.linuxidc.com/Linux/2015-08/122031.htm ,安装该软件之后才可以启用共享文件夹以利于RHEL6.5与windows系统进行文件交换。b、更新YUM源,RHEL和Centos都需要更新YUM源,操作步骤一致,YUM是一个链接到软件库的一个软件,随后安装软件需要用到。https://jingyan.baidu.com/article/b24f6c8239c6aa86bee5da60.html注意:该教程某些步骤可能会失效,需要结合自己具体的情况使用。安装好YUM之后,可以使用yum install gvim命令测试一下。c、安装GCC,G++,这两个软件在VCS+Verdi仿真时会调用到。命令:yum install gcc命令:yum install gcc-c++3、 Synopsys软件安装Synopsys软件安装教程,链接如下:https://wenku.baidu.com/view/c02c271d9b6648d7c0c74670.htmlhttp://bbs.eetop.cn/thread-553702-1-1.html高版本和低版本的Synopsy软件安装步骤一致,区别在于license的问题。用EETOP上的最新license即可使用15版的软件。在使用RHEL操作系统需要懂一些SHELL脚本,makefile脚本,这样便于提高操作效率,后文会提到。注意:此外还需要修改四个文件的hostname,使得这四处的hostname保持一致。a、synopsys.dat中的第一行hostname;b、synopsys.bashrc中的export SNPSLMD_LICENSE_FILE=27000@localhost行,“@”符号后的hostname;c、/etc/sysconfig/network配置文件中hostname;d、/etc/hosts配置文件中的127.0.0.1这一行的 ,第三个参数hostname;这四个hostname一定要一致,才能正确启动DC,PT,FM,ICC,VCS,VERDI软件。在启动DC,PT,FM,ICC,VCS,VERDI软件之前需要先启动Synopsys的license管理器。有关软件的使用教程可以参考官方的userguide。或者EETOP上,小伙伴们的教程。(三)工艺库说明(略,请点击阅读原文查看)(四)RTL设计数字电路设计RTL设计所需要的理论知识庞杂而繁多,本文所介绍的内容均由个人参阅了许多书籍之后加以整合的,很多内容本人也不是很熟,只是罗列出来作为参考学习的资料。主要有三个部分的内容,第一部分主要是数字电路设计的基础,这是在大学时期应该予以掌握的内容,第二部分是进阶的学习内容附带一个专业方向——MCU,第三部分是有关于各类算法处理的专业知识,需要更多的复合型知识,例如通信方向需要有较好的数学功底—傅立叶变换。由于这部分内容实在太多,个人没有能力也没有必要将每一部分的内容都详细的罗列出来,所以这里只是整理出一些需要把握的关键点。至于具体的内容,还请大家按照个人需求,参阅推荐的各类书籍。一、基础组合逻辑与时序逻辑:布尔代数,卡诺图,基本与非门,锁存器,触发器,冲突与冒险。——《Verilog HDL高级数字设计》Verilog语言基础:数值类型,表达式与运算符,assign语句,always语句,if-else语句,case语句,阻塞与非阻塞。——《Verilog HDL 硬件描述语言》状态机:一段式、二段式、三段式状态机的区别;独热码、二进制码、格雷码的区别及应用场合。——《Verilog HDL高级数字设计》同步电路和异步电路:两者的本质,异步电路跨时钟域,亚稳态。——IC_learner博客复位与时钟:同步复位、异步复位、异步复位同步释放的区别,时钟分频——二分频、三分频、任意整数分频,门控时钟,时钟切换。——《深入浅出玩转FPGA》,百度文档数据通路与控制通路:本质上任何数字电路都可以划分为简单的两种类型——控制通路与数据通路,控制通路的核心是状态机,数据通路是各类算术处理算法、并行总线等等。——《Verilog HDL高级数字设计》Testbench验证:无论什么电路,最终都需要验证其功能的正确性。Testbench的结构主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE等主要模块组成,其中,b是最重要的模块,一切验证都是从激励信号开始的。——《verilogHDL代码风格规范》。初学者推荐使用windows版qustasim 或者modelsim 仿真工具,简单又方便,以后可学习使用VCS+Verdi(比较折腾人)。二、进阶代码风格:良好的代码风格很有必要,参考一下企业用的代码风格,有助于个人养成良好的编码习惯。——《企业用verilog代码风格规范》《verilog语言编码风格》基本常用电路:具备以上庞杂的理论基础之后,需要积累一些常用的基础电路。——《华为Verilog典型电路设计》接口电路,I2C,UART,SPI:接口电路是中小规模芯片常用的对外接口电路,无论是与上位机(PC)通信还是控制其它芯片。I2C从机常用于EEPROM芯片中,主机可以直接使用单片机模拟,ARM单片机直接集成了I2C主机,I2C的IP代码网络上有现成的;UART是全双工电路,宏晶单片机通过UART进行烧录,SPI电路最常用于SD卡上。——《Verilog HDL高级数字设计》《通信IC设计(上下册)》有简单的UART和SPI的代码。RISC,8051 MCU ——IP:通过下载EETOP上相关的IP及文档来学习。 三、专业数值的表示方法:浮点数,定点数的表示办法——《Verilog HDL高级数字设计》《通信IC设计(上下册)》算术处理算法:浮点数的加法、乘法电路设计。——《Verilog HDL高级数字设计》通信算法:FIR滤波器,IIR滤波器,傅立叶变换,冗余编码等等各种通信方向必须掌握的。——《通信IC设计(上下册)》《数字信号处理的FPGA实现》图像处理算法:静态图像,动态图像去噪。——《数字图像处理与图像通信》SOC:SOC类芯片的组成结构,AMBA总线,IP复用,SV验证。——《Soc设计方法与实现》四、工具:文档代码编辑器:GVIM,Notpad++RTL设计规则检查:Nlin,spyglass(五)验证(1)一、前言借助于前文RTL设计中提到的UART代码,本章节将在后面给出对应的testbench以及说明如何在questa/modelsim、VCS+DVE、VCS+Verdi工具中使用。推荐书籍:《vcs User Guide 2016》二、TestbenchTestbench的结构,正如上文提到的,主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE,g,控制仿真时间这几个部分组成。本章节提供的testbench只包含a,b,e,f,g部分,至于c,d更高级的内容,暂时无法涉及,questa/modelsim将不会使用到e部分的代码,使用questa/modelsim仿真时要屏蔽掉全部e段的内容。同样,在使用VCS+DVE进行仿真时要屏蔽VCS+VERDI的e段内容三、工具使用3.1modelsim仿真对于modelsim仿真, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供)modelsim使用教程:https://wenku.baidu.com/view/db638e25b9d528ea81c779cc.html有关在modelsim软件中如何使用本示例请参考以上教程。仿真结果图:3.2 VCS+DVE和VCS+VERDI仿真对于VCS+DVE和VCS+VERDI, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供),3,包含verilog、testbench文件路径的uart.f文件(必要时需自行修改),4,makefile仿真启动文件。在终端中运行make命令即可运行仿真,一定要注意文件路径问题。makefile教程:http://blog.csdn.net/liang13664759/article/details/1771246VCS+DVE 使用教程,https://wenku.baidu.com/view/48912cf558fb770bf68a55b4.htmlDVE是VCS软件自带的波形查看器。本章实例对应的VCS+DVE makefile启动脚本:all:VCS DVE VCS: vcs -f uart.f -full64 -debug_all -R DVE: dve -vpd wave.vpd -mode64 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。uart.f内容:/home/Lance/synopsys/UART/testbench.v //必须放在文件中的第一行。/home/Lance/synopsys/UART/UART_XMTR.v/home/Lance/synopsys/UART/Control_Unit.v /home/Lance/synopsys/UART/Datapath_Unit.v/home/Lance/synopsys/UART/UART_RCVR.v/home/Lance/synopsys/UART/Control_Unit2.v/home/Lance/synopsys/UART/Datapath_Unit2.v DVE波形查看器启动命令:dve -vpd wave.vpd -mode64此外,在运行makefile启动脚本之前,还需要在testbench中添加如下代码:initialbegin $vcdplusfile("wave.vpd");//保存的波形文件名字 $vcdpluson(1,tb);//tb对应testbench文件的内的module名字 end该段代码为e,波形产生函数,主要是生成DVE波形查看器使用的VPD格式的波形文件。仿真结果图:VCS+Verdi,Verdi是debussy的升级版,是一个独立的软件,这对软件组合使用方式与VCS+DVE差不多。VCS+Verdi makefile启动脚本:all:VCS VERDI VCS:vcs +v2k -sverilog -debug_all -P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a +vcs+lic+wait \ -f uart.f -y ./ +libext+.v -full64 -RVERDI: verdi -f uart.f -ssf wave.fsdb & 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。注意:-P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a主要是调用Verdi的接口函数以生成fsdb波形。 Verdi波形查看器启动命令:verdi -f uart.f -ssf wave.fsdb &此外,在运行makefile启动命令前,还需要在testbench中添加如下代码:initialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars(0,tb); end 以生成Verdi波形查看器使用的FSDB格式的波形文件。注意: 启动脚本相关问题,需要学习makefile有关内容,有关VCS和Verdi的详细使用教程,还请参考其它资料。 (七) 综合(八)形式验证(九)数模混合仿真(十)静态时序分析(十一)低功耗设计(十二)可测性设计(由于篇幅关系,以上章节请点击阅读原文前往作者博客查看)推荐阅读:关注EETOP公众号,后台输入 芯片,查看如下文章ASIC前后端设计经典的细节讲解IC大牛10多年的设计分享:数字典型电路知识结构地图及代码实现关于华为海思,这篇文章值得一看俄国没有高端芯片,为什么却能造出一流武器?别拦我,我要做芯片!芯片春秋·ARM传中国芯酸往事印度芯酸往事国防军工芯片行业深度报告一位美国芯片公司华人高管对中国芯片行业的思考学习、积累、交流-IC设计高手的成长之路女生学微电子是一种什么体验?MIPS架构开放了,10天设计一款完全免费的MIPS处理器(附源码)性能之殇:从冯·诺依曼瓶颈谈起AI芯片设计与开发概览AI 芯片和传统芯片有何区别?一个资深工程师老王关于AI芯片的技术感悟隔隔壁老王:AI芯片与她怎么选?终于有人把云计算、大数据和人工智能讲明白了!尺寸减半、功率翻番!——氮化镓技术的现在和未来逻辑综合 Design Compiler 资料大全集成电路制造技术简史版图中Metal专题——线宽选择麒麟980内核照片:NPU在哪呢?有哪些只有IC工程师才能get到的梗?为什么7nm工艺制程这么难?从7nm看芯片行业的“贫富差距”什么是台积电的SoIC? RISC-V打入主流市场的诸多问题RISC-V架构有何优势?关于RISC-V 终于有人讲明白了!ASIC低功耗设计实例分析及书籍推荐ASIC设计学习总结之可测性设计及书籍推荐ASIC设计学习总结之静态时序分析概要及书籍推荐ASIC设计学习总结之工具及书籍文档小芯片大价值 | ASIC工程师如此值钱到底为什么?芯片面积估计方法简介自主研发通信芯片有多难?通信行业老兵告诉你,没那么简单!RISC-V精简到何种程度?能省的都省了!多核CPU设计及RISC-V相关资料时序设计与约束资料汇总模拟版图讲义GDSII转DEF的flow简介机器学习将越来越依赖FPGA和SoCVerilog基本功之:流水线设计Pipeline Design先进封装发展趋势分析PPT先进封装发展现状分析PPT可测试性设计与ATPG麒麟980是如何诞生的?敢于失败,勇于尝试!(附:华为早期型号处理器研发过程)IC模拟版图设计讲义 Verilog CPU设计实例。。。。(共260篇)

ASIC设计学习总结(包括:工具及书籍文档推荐 、软件环境搭建、RTL设计、验证、工艺库说明、形式验证、综合等共12部分) 原创tfpwl——lj EET0P2019年02月07日09:57之前介绍过了了芯片设计全流程介绍(芯片设计全流程详解 包括:正向流程和反向流程)。由于当时的经验十分有限,所以对于正向设计,特别是对于从RTL级代码开始的设计介绍得不是很清楚。经过这一段时间的学习,对于从RTL级代码开始的Asic芯片设计有了更多的认识,现在总结一下,一方面给自己整理思路,另一方面也希望抛砖引玉,让大家各抒己见,分享一下各自的设计经验,促进我们的共同进步。笔者原本打算详细的介绍学习中的收获,将各类知识点写成文章,但经过反复考量之后,发现这种详细照搬别人知识的做法其实没什么意思。与其原封不动的转述别人书中的内容,不如直接提供参阅的书目,这样就免得在转述别人的知识的时候误解作者想要表达的真正意义。所以本系列的文章,笔者将个人学习的经验加以整合,将经验知识点罗列出来,并附加所参阅的书籍。另外涉及到实践操作过程的章节,将会把具体使用的工具罗列出来,并附上一些参考性的代码和脚本。本系列文章主要分为十二个部分,分别为:(一)工具及书籍文档推荐(二)软件环境搭建(三)RTL设计(四)验证(五)工艺库说明(六)形式验证(七)综合(八)可测性设计(九)低功耗设计(十)静态时序分析(十一)数模混合仿真(十二)可测性设计介绍这么多,不是显得个人有多少经验,其实本人也只是菜鸟,关注这么多内容,主要是为了让自己的知识储备更全面一下,这样考虑设计问题的时候遗漏的东西会更少一些。在本系列文章中,每个章节的详略是不同的,主要是跟个人工作经验有关,有介绍得简单的地方,麻烦大家帮忙补充。每个部分的内容基本采用“理论+工具+示例”的行文结构,有些EDA工具笔者没有使用过的就暂不能提供实例了。(一)工具及书籍文档一、前言对于RTL级的Asic设计所涉及到的软件是非常之多的,笔者也并没有每一个都使用过。二、工具介绍RTL代码规则检查工具:nlint,spyglass。这两个软件主要是用于检查代码的语法和语义错误的,并且比其他的工具能检测出更多的问题,比如说命名规格,时序风险,功耗等。详细介绍请参考软件的使用教程,nlint有Windows版和linux版,软件的linux版本和使用教程可以在eetop上搜索到。RTL代码仿真工具:这类仿真工具有较多的组合,比如说:qustasim/modelsim,NC_verilog+Verdi,VCS+DVE,VCS+Verdi等等。目前笔者使用的组合是VCS+Verdi。这两个软件是业内主流的仿真软件,还可以结合UVM库进行仿真,当然这是验证方法学的内容。综合工具:Design Complier。最常用的综合工具,没有之一,该软件主要是将RTL代码“翻译+优化+映射”成与工艺库对应的门级网表。并且还包含功耗分析软件Power Complier和边界扫描寄存器插入软件 BSD Complier。可测性设计:DFT Complier + TetraMAX。软件在DC之后使用,DFT Complier 用于将设计的内部寄存器替换成扫描寄存器并组成一条或多条扫描链,TetraMAX是用于自动生成测试向量的。形式验证工具:Formality、Conforml(candence出品)。等价性验证工具,主要是在DFT Complier插入扫描链之后进行验证,另外,在版图综合时钟树,插入BUFFER之后,也需要用该工具进行等效性验证。静态时序分析工具: Prime Time。业界最常用的时序分析工具之一,该软件包括功耗分析PTPX工具,功耗分析必备。cadence也有对应的时序分析工具——Encounter Timing System。自动布局布线工具(APR):ICC,Enconter。其中Encounter是Cadence公司的。数模混合仿真: nanosim + VCS,nanosim的升级版为XA。这是一篇有关于synopsysEDA工具软件的介绍,希望对于EDA软件的用途不清楚的伙伴有帮助。http://bbs.eetop.cn/thread-151171-1-1.html三、书籍推荐《Verilog HDL 硬件描述语言》《设计与验证Verilog HDL》《企业用verilog代码风格规范》《verilog语言编码风格》《verilogHDL代码风格规范》《Verilog HDL高级数字设计》《Soc设计方法与实现》《高级ASIC芯片综合》《华为Verilog典型电路设计》《数字IC系统设计》《数字集成电路--电路、系统与设计》《专用集成电路设计实用教程》《集成电路静态时序分析与建模》《CMOS集成电路后端设计与实战》《makefile教程》《鸟哥的私房菜》《SystemVerilog与功能验证》《UVM实战》《通信IC设计(上下册)》《数字图像处理与图像通信》《数字信号处理的FPGA实现中文版》各类Synopsy userguide,EETOP有16年版的。三、工艺库说明使用DC,PT,FM,ICC或者ENCOUNTER软件需要工艺库文件,主要包括数字逻辑单元文件,符号库,综合库,寄生电容参数库,版图文件LEF,milkway库等等。有关工艺库各文件夹的作用,笔者将会在将“工艺库说明”的章节进行详细介绍,如果有遗漏还请大家包涵。(二)环境搭建一、前言先介绍一下个人的使用环境。由于网络上已经存在很多安装教程,笔者就不再废话,直接给出他们的连接,并附带其他需要注意的关键点,如果有安装问题,请追问。Synopsys软件安装包下载地址在笔者前一篇文章“工具及书籍文档”,都是来自EETOP的大牛们提供的。在安装的过程中需要具备一些Linux系统的使用经验,不然会很难理解这些步骤是做什么的。个人的环境如下:1、vmware 12;2、RHEL6.5系统;3、synopsys软件,Lib Complier,VCS,Verdi,Desgin Complier,PrimeTime,Formality,ICC。一共7个软件,几乎都是15年版本的。二、步骤环境搭建需要准备以下三件事:1,vmware12虚拟机安装;安装教程如下。https://jingyan.baidu.com/article/215817f78879c21edb142379.html2, RHEL6.5操作系统安装,当然也可以使用CentOs6.5,安装教程如下。http://www.linuxidc.com/Linux/2016-05/131701.htm ——》RHEL6.5https://www.kafan.cn/edu/488101.html ——》Centos6.5a、安装vmware tools。在虚拟机中把系统安装好了之后,需要安装vmware tools,安装教程如下,http://www.linuxidc.com/Linux/2015-08/122031.htm ,安装该软件之后才可以启用共享文件夹以利于RHEL6.5与windows系统进行文件交换。b、更新YUM源,RHEL和Centos都需要更新YUM源,操作步骤一致,YUM是一个链接到软件库的一个软件,随后安装软件需要用到。https://jingyan.baidu.com/article/b24f6c8239c6aa86bee5da60.html注意:该教程某些步骤可能会失效,需要结合自己具体的情况使用。安装好YUM之后,可以使用yum install gvim命令测试一下。c、安装GCC,G++,这两个软件在VCS+Verdi仿真时会调用到。命令:yum install gcc命令:yum install gcc-c++3、 Synopsys软件安装Synopsys软件安装教程,链接如下:https://wenku.baidu.com/view/c02c271d9b6648d7c0c74670.htmlhttp://bbs.eetop.cn/thread-553702-1-1.html高版本和低版本的Synopsy软件安装步骤一致,区别在于license的问题。用EETOP上的最新license即可使用15版的软件。在使用RHEL操作系统需要懂一些SHELL脚本,makefile脚本,这样便于提高操作效率,后文会提到。注意:此外还需要修改四个文件的hostname,使得这四处的hostname保持一致。a、synopsys.dat中的第一行hostname;b、synopsys.bashrc中的export SNPSLMD_LICENSE_FILE=27000@localhost行,“@”符号后的hostname;c、/etc/sysconfig/network配置文件中hostname;d、/etc/hosts配置文件中的127.0.0.1这一行的 ,第三个参数hostname;这四个hostname一定要一致,才能正确启动DC,PT,FM,ICC,VCS,VERDI软件。在启动DC,PT,FM,ICC,VCS,VERDI软件之前需要先启动Synopsys的license管理器。有关软件的使用教程可以参考官方的userguide。或者EETOP上,小伙伴们的教程。(三)工艺库说明(略,请点击阅读原文查看)(四)RTL设计数字电路设计RTL设计所需要的理论知识庞杂而繁多,本文所介绍的内容均由个人参阅了许多书籍之后加以整合的,很多内容本人也不是很熟,只是罗列出来作为参考学习的资料。主要有三个部分的内容,第一部分主要是数字电路设计的基础,这是在大学时期应该予以掌握的内容,第二部分是进阶的学习内容附带一个专业方向——MCU,第三部分是有关于各类算法处理的专业知识,需要更多的复合型知识,例如通信方向需要有较好的数学功底—傅立叶变换。由于这部分内容实在太多,个人没有能力也没有必要将每一部分的内容都详细的罗列出来,所以这里只是整理出一些需要把握的关键点。至于具体的内容,还请大家按照个人需求,参阅推荐的各类书籍。一、基础组合逻辑与时序逻辑:布尔代数,卡诺图,基本与非门,锁存器,触发器,冲突与冒险。——《Verilog HDL高级数字设计》Verilog语言基础:数值类型,表达式与运算符,assign语句,always语句,if-else语句,case语句,阻塞与非阻塞。——《Verilog HDL 硬件描述语言》状态机:一段式、二段式、三段式状态机的区别;独热码、二进制码、格雷码的区别及应用场合。——《Verilog HDL高级数字设计》同步电路和异步电路:两者的本质,异步电路跨时钟域,亚稳态。——IC_learner博客复位与时钟:同步复位、异步复位、异步复位同步释放的区别,时钟分频——二分频、三分频、任意整数分频,门控时钟,时钟切换。——《深入浅出玩转FPGA》,百度文档数据通路与控制通路:本质上任何数字电路都可以划分为简单的两种类型——控制通路与数据通路,控制通路的核心是状态机,数据通路是各类算术处理算法、并行总线等等。——《Verilog HDL高级数字设计》Testbench验证:无论什么电路,最终都需要验证其功能的正确性。Testbench的结构主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE等主要模块组成,其中,b是最重要的模块,一切验证都是从激励信号开始的。——《verilogHDL代码风格规范》。初学者推荐使用windows版qustasim 或者modelsim 仿真工具,简单又方便,以后可学习使用VCS+Verdi(比较折腾人)。二、进阶代码风格:良好的代码风格很有必要,参考一下企业用的代码风格,有助于个人养成良好的编码习惯。——《企业用verilog代码风格规范》《verilog语言编码风格》基本常用电路:具备以上庞杂的理论基础之后,需要积累一些常用的基础电路。——《华为Verilog典型电路设计》接口电路,I2C,UART,SPI:接口电路是中小规模芯片常用的对外接口电路,无论是与上位机(PC)通信还是控制其它芯片。I2C从机常用于EEPROM芯片中,主机可以直接使用单片机模拟,ARM单片机直接集成了I2C主机,I2C的IP代码网络上有现成的;UART是全双工电路,宏晶单片机通过UART进行烧录,SPI电路最常用于SD卡上。——《Verilog HDL高级数字设计》《通信IC设计(上下册)》有简单的UART和SPI的代码。RISC,8051 MCU ——IP:通过下载EETOP上相关的IP及文档来学习。 三、专业数值的表示方法:浮点数,定点数的表示办法——《Verilog HDL高级数字设计》《通信IC设计(上下册)》算术处理算法:浮点数的加法、乘法电路设计。——《Verilog HDL高级数字设计》通信算法:FIR滤波器,IIR滤波器,傅立叶变换,冗余编码等等各种通信方向必须掌握的。——《通信IC设计(上下册)》《数字信号处理的FPGA实现》图像处理算法:静态图像,动态图像去噪。——《数字图像处理与图像通信》SOC:SOC类芯片的组成结构,AMBA总线,IP复用,SV验证。——《Soc设计方法与实现》四、工具:文档代码编辑器:GVIM,Notpad++RTL设计规则检查:Nlin,spyglass(五)验证(1)一、前言借助于前文RTL设计中提到的UART代码,本章节将在后面给出对应的testbench以及说明如何在questa/modelsim、VCS+DVE、VCS+Verdi工具中使用。推荐书籍:《vcs User Guide 2016》二、TestbenchTestbench的结构,正如上文提到的,主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE,g,控制仿真时间这几个部分组成。本章节提供的testbench只包含a,b,e,f,g部分,至于c,d更高级的内容,暂时无法涉及,questa/modelsim将不会使用到e部分的代码,使用questa/modelsim仿真时要屏蔽掉全部e段的内容。同样,在使用VCS+DVE进行仿真时要屏蔽VCS+VERDI的e段内容三、工具使用3.1modelsim仿真对于modelsim仿真, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供)modelsim使用教程:https://wenku.baidu.com/view/db638e25b9d528ea81c779cc.html有关在modelsim软件中如何使用本示例请参考以上教程。仿真结果图:3.2 VCS+DVE和VCS+VERDI仿真对于VCS+DVE和VCS+VERDI, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供),3,包含verilog、testbench文件路径的uart.f文件(必要时需自行修改),4,makefile仿真启动文件。在终端中运行make命令即可运行仿真,一定要注意文件路径问题。makefile教程:http://blog.csdn.net/liang13664759/article/details/1771246VCS+DVE 使用教程,https://wenku.baidu.com/view/48912cf558fb770bf68a55b4.htmlDVE是VCS软件自带的波形查看器。本章实例对应的VCS+DVE makefile启动脚本:all:VCS DVE VCS: vcs -f uart.f -full64 -debug_all -R DVE: dve -vpd wave.vpd -mode64 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。uart.f内容:/home/Lance/synopsys/UART/testbench.v //必须放在文件中的第一行。/home/Lance/synopsys/UART/UART_XMTR.v/home/Lance/synopsys/UART/Control_Unit.v /home/Lance/synopsys/UART/Datapath_Unit.v/home/Lance/synopsys/UART/UART_RCVR.v/home/Lance/synopsys/UART/Control_Unit2.v/home/Lance/synopsys/UART/Datapath_Unit2.v DVE波形查看器启动命令:dve -vpd wave.vpd -mode64此外,在运行makefile启动脚本之前,还需要在testbench中添加如下代码:initialbegin $vcdplusfile("wave.vpd");//保存的波形文件名字 $vcdpluson(1,tb);//tb对应testbench文件的内的module名字 end该段代码为e,波形产生函数,主要是生成DVE波形查看器使用的VPD格式的波形文件。仿真结果图:VCS+Verdi,Verdi是debussy的升级版,是一个独立的软件,这对软件组合使用方式与VCS+DVE差不多。VCS+Verdi makefile启动脚本:all:VCS VERDI VCS:vcs +v2k -sverilog -debug_all -P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a +vcs+lic+wait \ -f uart.f -y ./ +libext+.v -full64 -RVERDI: verdi -f uart.f -ssf wave.fsdb & 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。注意:-P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a主要是调用Verdi的接口函数以生成fsdb波形。 Verdi波形查看器启动命令:verdi -f uart.f -ssf wave.fsdb &此外,在运行makefile启动命令前,还需要在testbench中添加如下代码:initialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars(0,tb); end 以生成Verdi波形查看器使用的FSDB格式的波形文件。注意: 启动脚本相关问题,需要学习makefile有关内容,有关VCS和Verdi的详细使用教程,还请参考其它资料。 (七) 综合(八)形式验证(九)数模混合仿真(十)静态时序分析(十一)低功耗设计(十二)可测性设计(由于篇幅关系,以上章节请点击阅读原文前往作者博客查看)推荐阅读:关注EETOP公众号,后台输入 芯片,查看如下文章ASIC前后端设计经典的细节讲解IC大牛10多年的设计分享:数字典型电路知识结构地图及代码实现关于华为海思,这篇文章值得一看俄国没有高端芯片,为什么却能造出一流武器?别拦我,我要做芯片!芯片春秋·ARM传中国芯酸往事印度芯酸往事国防军工芯片行业深度报告一位美国芯片公司华人高管对中国芯片行业的思考学习、积累、交流-IC设计高手的成长之路女生学微电子是一种什么体验?MIPS架构开放了,10天设计一款完全免费的MIPS处理器(附源码)性能之殇:从冯·诺依曼瓶颈谈起AI芯片设计与开发概览AI 芯片和传统芯片有何区别?一个资深工程师老王关于AI芯片的技术感悟隔隔壁老王:AI芯片与她怎么选?终于有人把云计算、大数据和人工智能讲明白了!尺寸减半、功率翻番!——氮化镓技术的现在和未来逻辑综合 Design Compiler 资料大全集成电路制造技术简史版图中Metal专题——线宽选择麒麟980内核照片:NPU在哪呢?有哪些只有IC工程师才能get到的梗?为什么7nm工艺制程这么难?从7nm看芯片行业的“贫富差距”什么是台积电的SoIC? RISC-V打入主流市场的诸多问题RISC-V架构有何优势?关于RISC-V 终于有人讲明白了!ASIC低功耗设计实例分析及书籍推荐ASIC设计学习总结之可测性设计及书籍推荐ASIC设计学习总结之静态时序分析概要及书籍推荐ASIC设计学习总结之工具及书籍文档小芯片大价值 | ASIC工程师如此值钱到底为什么?芯片面积估计方法简介自主研发通信芯片有多难?通信行业老兵告诉你,没那么简单!RISC-V精简到何种程度?能省的都省了!多核CPU设计及RISC-V相关资料时序设计与约束资料汇总模拟版图讲义GDSII转DEF的flow简介机器学习将越来越依赖FPGA和SoCVerilog基本功之:流水线设计Pipeline Design先进封装发展趋势分析PPT先进封装发展现状分析PPT可测试性设计与ATPG麒麟980是如何诞生的?敢于失败,勇于尝试!(附:华为早期型号处理器研发过程)IC模拟版图设计讲义 Verilog CPU设计实例。。。。(共260篇)