SOP( Small Outline Package )小外形封装,指鸥翼形 (L 形 )引线从封装的两个侧面引出的一 种表面贴装型封装。 1968 ~ 1969 年飞利浦公司就开发出小外形封装( SOP)。以后逐渐派生出 SOJ( J 型引脚小 外形封装) 、TSOP(薄小外形封装) 、VSOP (甚小外形封装) 、SSOP(缩小型 SOP)、TSSOP(薄 的缩小型 SOP)及 SOT(小外形晶体管) 、 SOIC (小外形集成电路)等。在引脚数量不超过 40 的领域, SOP 是普及最广的表面贴装封装,典型引脚中心距 1.27mm(50mil) ,其它有 0.65mm 、 0.5mm ;引脚数多为 8~ 32;装配高度不到 1.27mm 的 SOP 也称为 TSOP 。

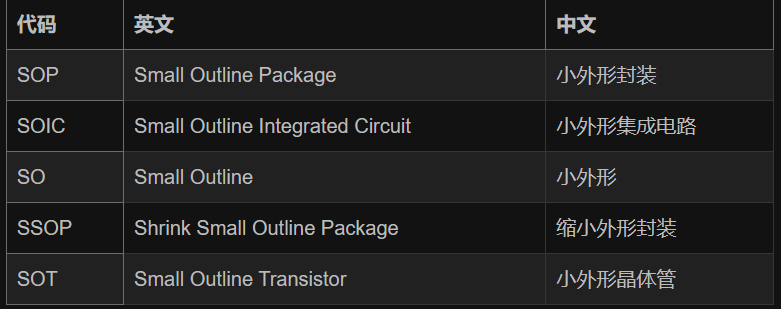

表 1、常用缩写代码含义

二、宽体、中体、窄体以及 SO、SOP、SOIC之争。

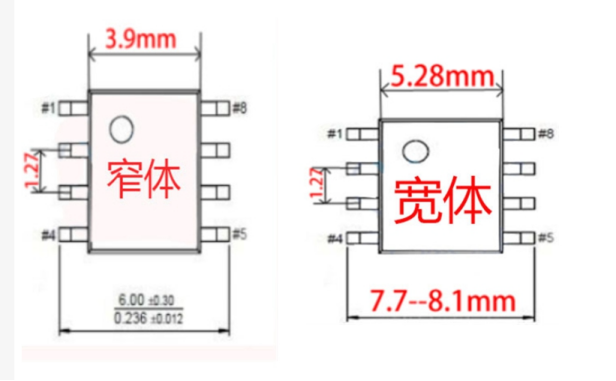

在事实上,针对 SOIC 封装的尺寸标准,不同的厂家分别或同时遵循了两种不同的标准 JEDEC (美国联合电子设备工程委员会)和 EIAJ (日本电子机械工业协会),结果就导致了“宽体、中体和窄体”三个分支概念的出现,把很多人搞得晕头转向,也激起很多砖家在“宽体、中体、窄体以及 SO、SOP、SOIC ”几个概念之间争得死去活来。 还有许多来自不同半导体制造商的封装不属于上述标准。 另外, JEDEC 和 EIAJ 这两种标准 的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系 统也不统一。 其实,静下心来,仔细看一下两个封装标准,再对比几种常见的元件尺寸,不难发现,规律其实并不复杂:

1、 单从字面上理解,其实 SO=SOP=SOIC 。

2、 混乱现象主要出现在管脚间距 1.27mm 的封装上,多为 74 系列的数字逻辑芯片。

3、 两个标准对代码缩写各有自己的习惯:

EIAJ 习惯上使用 SOP( 5.3mm 体宽);

JEDEC 习惯上使用 SOIC ( 3.9mm 与 7.5mm 两种体宽);

也有些公司并不遵守这个习惯,如 UTC ,使用 SOP( 3.9mm 与 7.5mm 两种体宽);

另有很多制造商使用 SO、 DSO、 SOL 等。

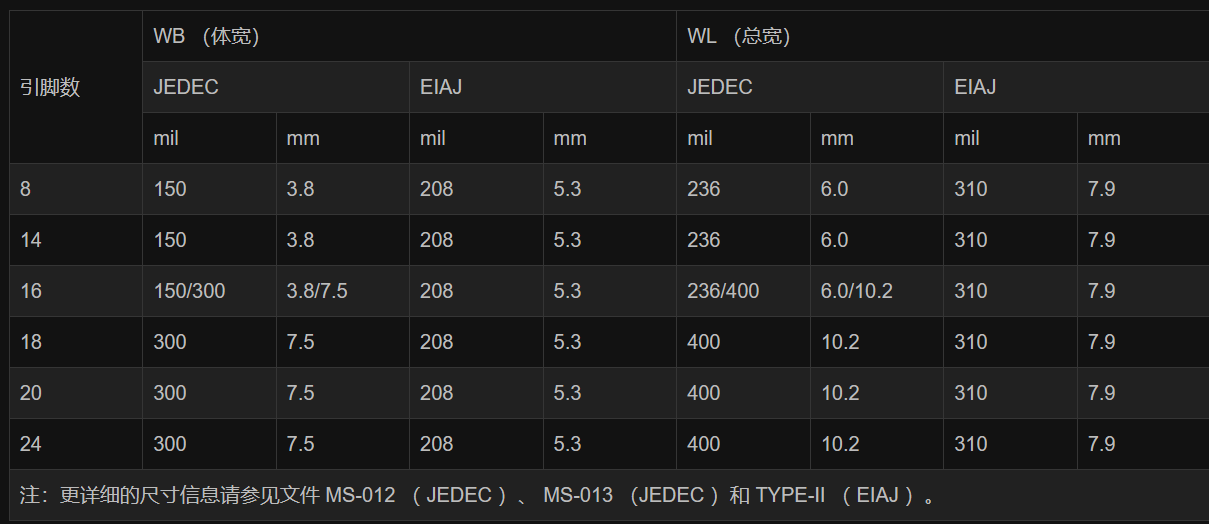

4、 两个标准规定的尺寸不同,互不兼容,其差异主要体现在宽度 WB 和 WL 上,下表给出了常用 SOP 封装在两个标准下的 WB 与 WL 值:

表 2、 SOP 封装在 JEDEC 和 EIAJ 标准下的尺寸差异

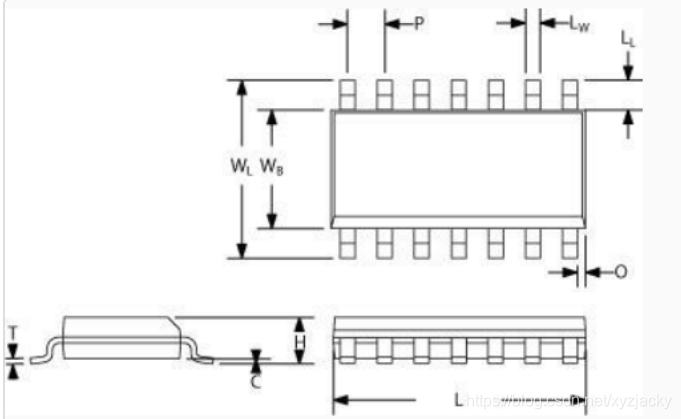

其中 WB 与 WL 的含义如下:

名词解释

它们之间主要有两点区别:

相邻引脚中心间距;

相对引脚中心间距。

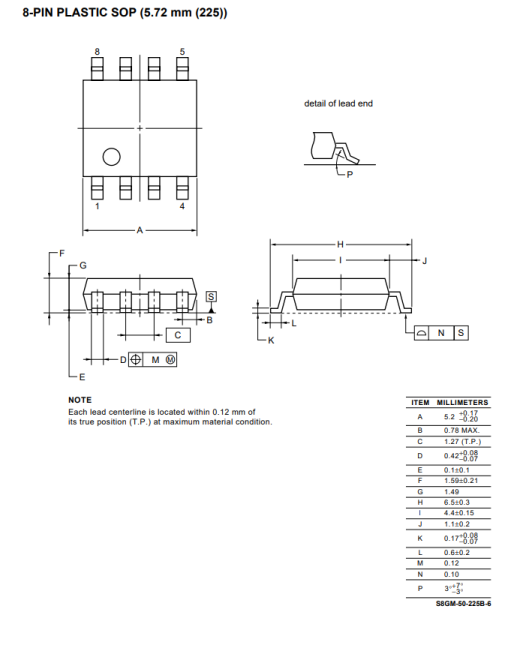

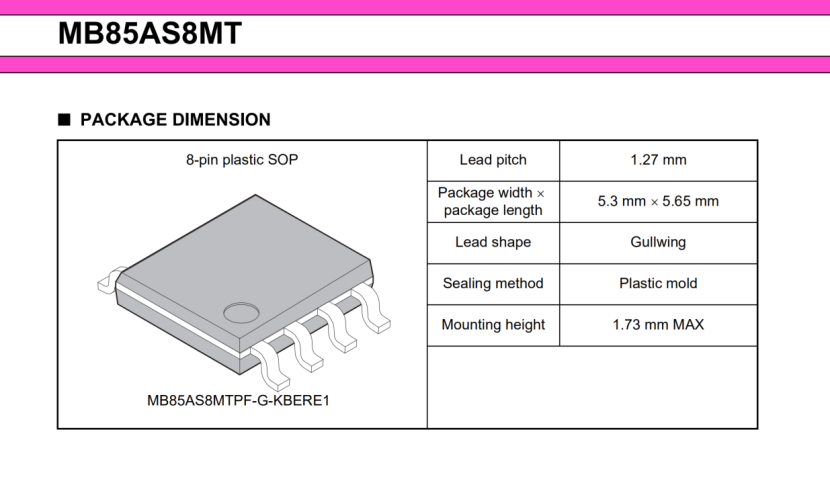

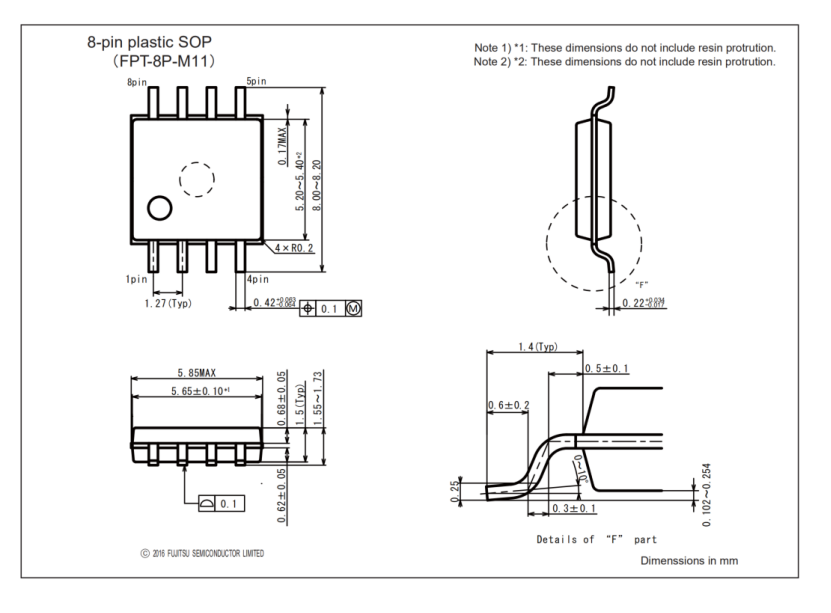

8-pin plastic SOP

评论 (0)