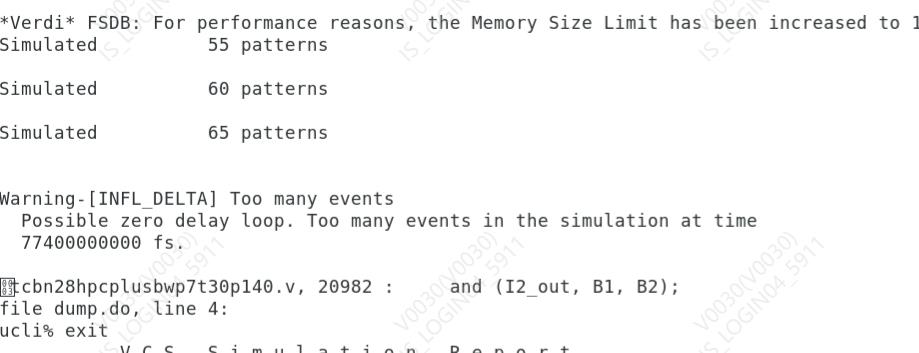

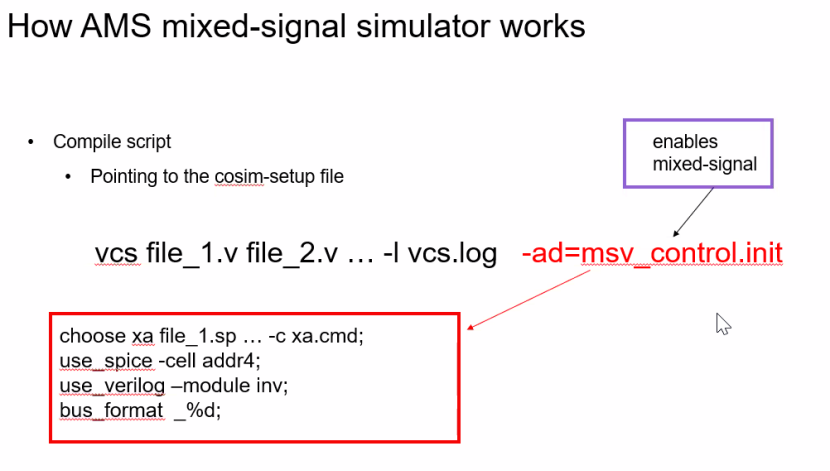

当仿真出现如下的提示,说明遇到了 loop,可以在 vcs compile option 中用

+vcs+loopreport 来报 loop 的点,但耗时较长并且报出来的位置不精准,遇到这种情

况,可以用下面这种方法来快速定位 loop 的位置

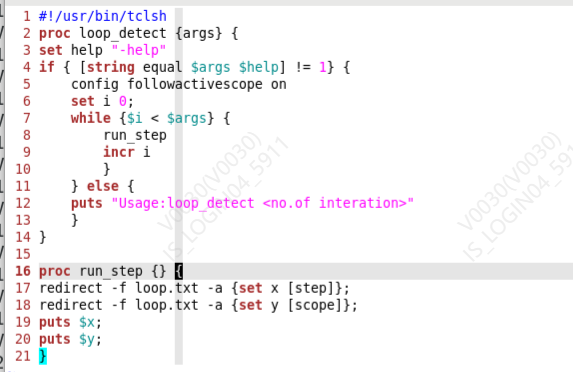

- 创建 loop_detect.tcl,放在仿真目录。脚本内容如下:

2.增加 compile option:

-debug_all

3.正常执行仿真,当出现 loop 信息时 ctrl+c 暂停后执行

source loop_detect.tcl

- 执行 loop_detect 1000(1000 可以修改,num 越大,打印的信息越多)

- 执行完成后在仿真目录下会生成一个 loop.txt 文件

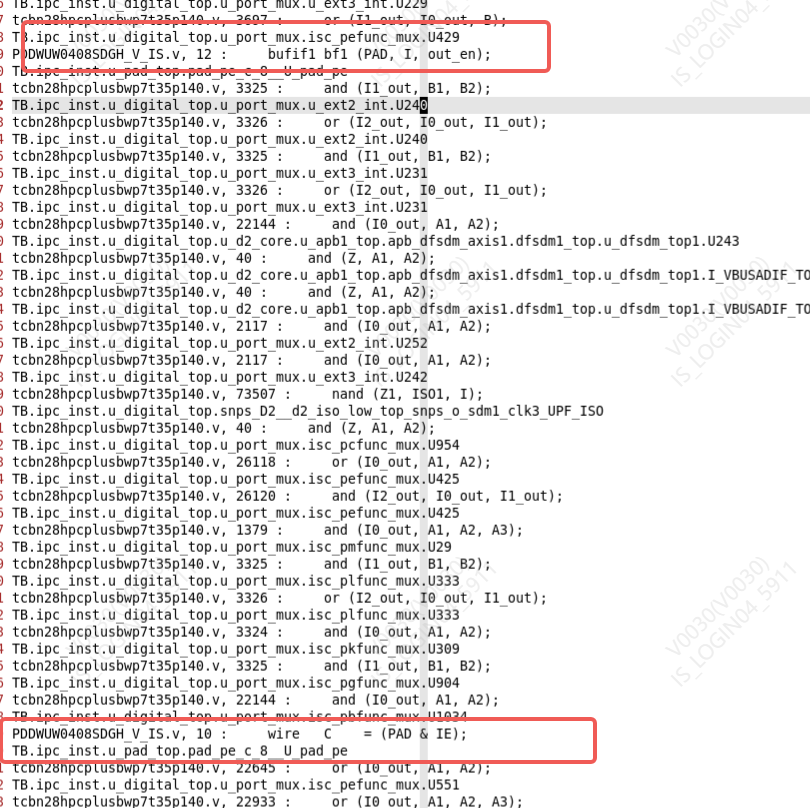

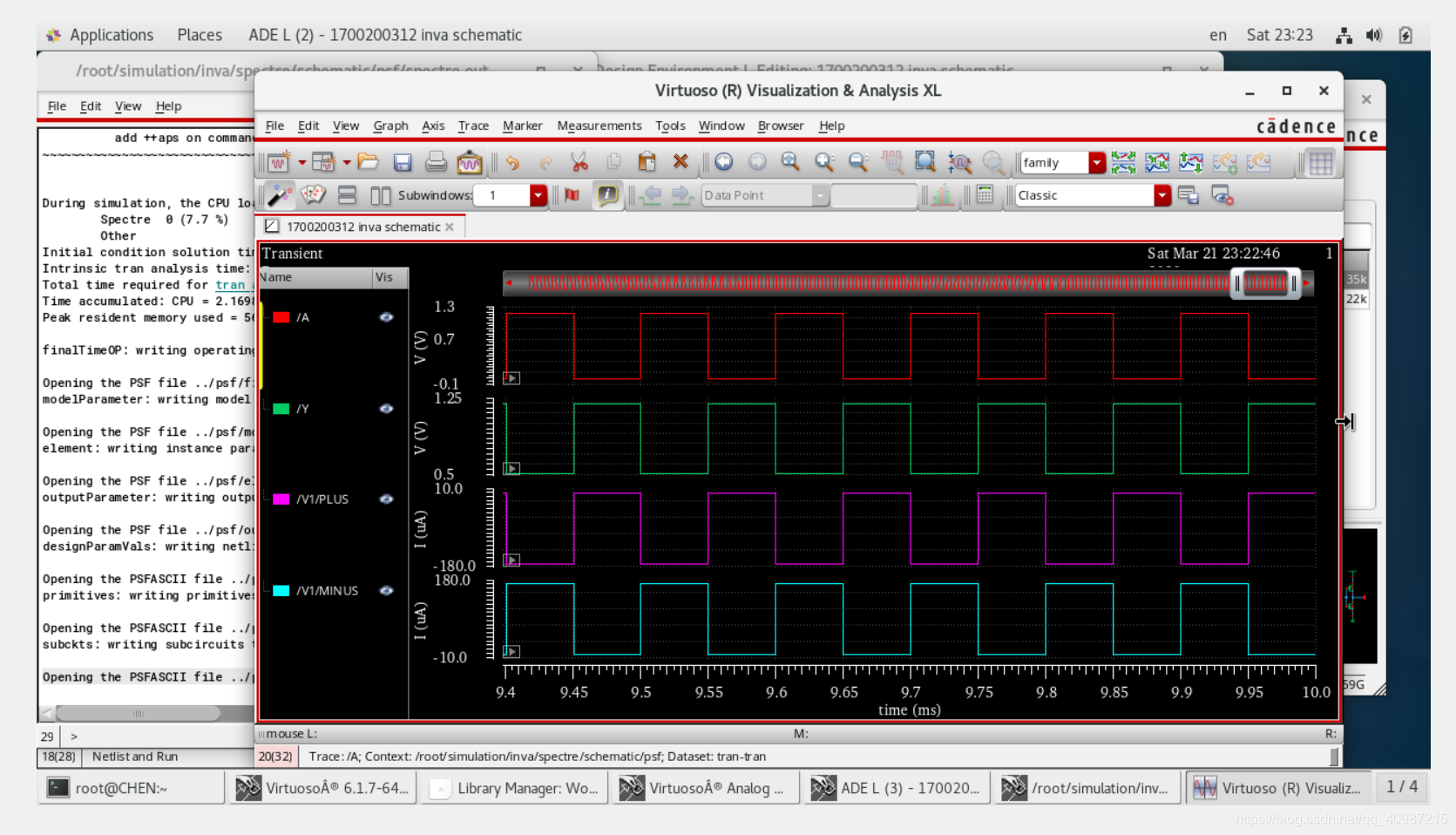

这里发现是在 pad 中发生了 loop,将 pad 的 IE force 成 0 继续往下跑,loop 被打断,

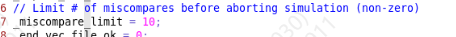

因为 force 的原因会出现 mismatch,当 mismatch 数量超过 10 个会退出仿真,为了让

仿真跑完可以把 tb 里的_miscompare_limit 限制改大一点,让它继续往下跑。

每次出现 loop 都完成上述 1-5 的操作,直到所有的 loop 打断(miamatch 不用管)。将

所有的 loop 点记录下来后,去 flow 中做 eco,重新跑 atpg,再仿真,就全部 pass

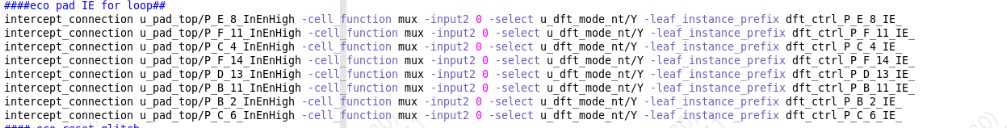

了。最终 eco 的 loop 点有

评论 (0)