在芯片验证的仿真中,有时候需要从文件中加载一些数据,比如激励、初始化数据、code等等,这些文件路径可以用绝对路径,当然为了其他人也可以用,最好用相对路径,这就需要用到环境变量来做路径的前半段。

在module中得到或设置系统环境变量需要用到systemverilog的DPI-C,import C函数,然后在module中的块语句中调用C函数。

步骤如下:

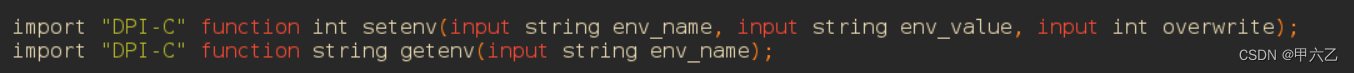

- 在要获得环境变量的文件中 import setenv和getenv

如下所示,把这两个函数import进去,不需要定义对应的C函数

import "DPI-C" function int setenv(input string env_name, input string env_value, input int overwrite);

import "DPI-C" function string getenv (input string env_name);

- 直接使用getenv, setenv来获得和设置环境变量

module mem read(

input [8*200-1: O] mem_file

);

initial begin

$display("mem_file is %Os", mem_file);

end

endmodule

module dut (

input clk,

input wire [31:0]addr,

output [31:0] rdata,

input [31:0] wdata,

input wire wr

);

string path;

initial begin

setenv("PRJDIR", "/project/uart", 1);

path = getenv( "PRJDIR");

$display("PRJDIR is %Os", path);

setenv( "PRJDIR", "/project/sp", 1);

path = getenv( "PRJDIR");

$display("PRJDIR is %0s", path);

end

mem_read u_mem_rd(.mem_file(path));

endmodule

————————————————

版权声明:本文为CSDN博主「甲六乙」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/m0_38037810/article/details/126136552

评论 (0)