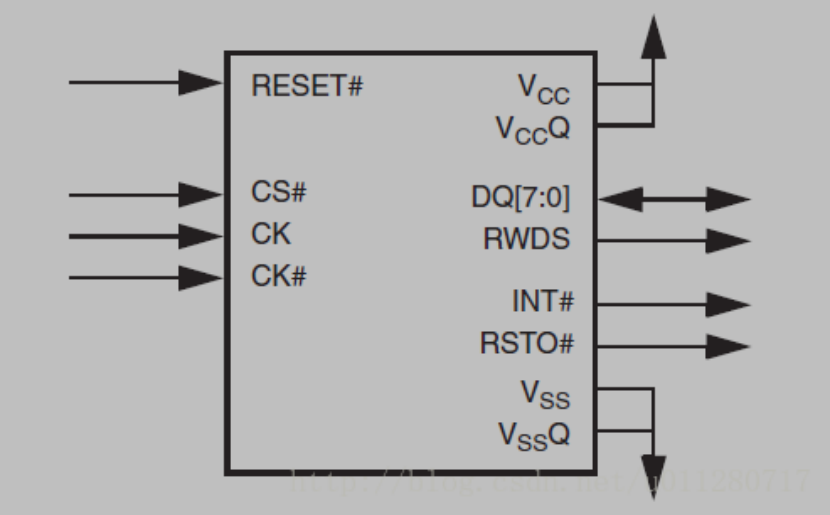

Interface

Mandatory I/O Summary

Optional I/O Summary

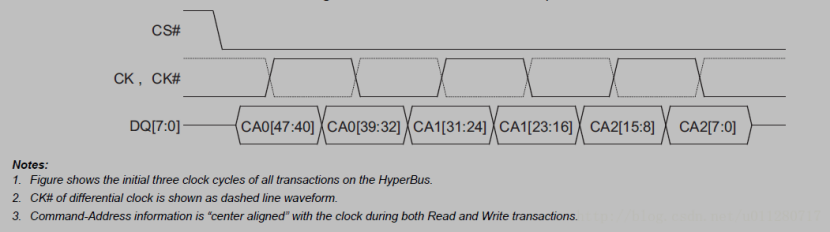

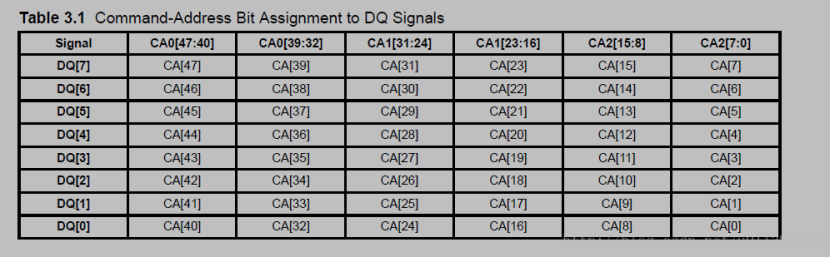

Protocal

当HyperBus处于Idle状态(CK=Low & CK#=High)时,CS#从High变成Low,hyperbus的传输开始进行。最前面的三个时钟周期传输3个word的Command/Address(CA0, CA1, CA2),这三个word的CA用来决定这个传输一些特性。

PS:这里面的word是2个byte,就是16bit。一个时钟周期是指两个clock,至于为什么这样定,我也不知道,Hyperbus的specification就是这么定的

所以3个word的CA信息一共是48个bit。

当传输完CA信息后,bus上需要传输一些dummy clock初始化RWDS信号。RWDS就是CK加了一些延迟的信号,用作高速读操作时的DQS。

当数据传输开始,读数据是在RWDS的边沿进行采样,写数据是在Single-ended clock(即3.0V的CK)的边沿采样,或者在Differential clock(即1.8V CK和CK#)模式下,在CK和CK#交叉点进行数据采样。

一旦完成数据传输,host就可以把CS#拉高并且把clock置为IDLE状态。当clock已经是IDLE状态了,拉嘎CS#就能结束一次传输。

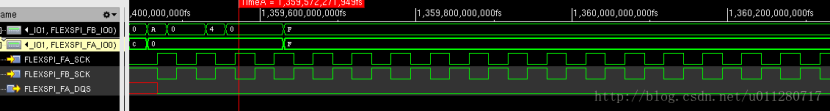

读时序

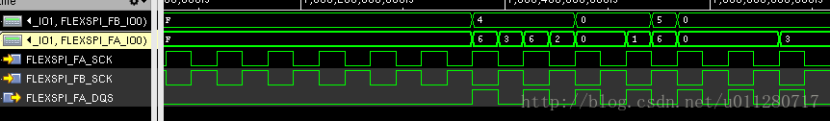

下面贴出一个实际的读数据的时序, 读数据的地址是0x400。CA[48:0] = 0xA000004000。其中CA[47] = 1代表读,CA[46] = 0, CA[45] =1代表linear burst,ROW & Upper Column Address = 0x0000040 = 0x400 / 0x10, Lower Column Address=0x0 = 0x400 % 0x10。在插入了一些dummy的时钟周期后,进行了数据的采集。

其中, 插入在CA和数据之间的dummy clock的个数是随设备不同而不同的,同时也跟Hyperbus的采样频率有关,这个需要参考不同的Hyberbus设备的手册才能知道。

写时序

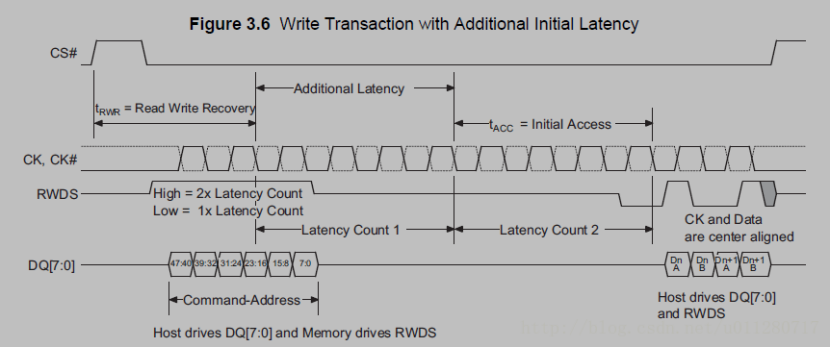

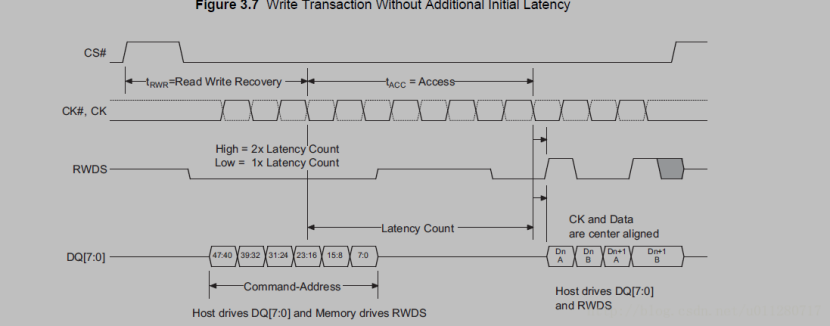

写时序分为Write Transactions with Initial Latency和Write Transactions without Initial Latency。由于我并没有涉及太多的写设备的工作,所以这里就不多讲了。有Initial Latency的时序跟读时序差不多,只不过需要注意的是采样的时钟并不是RWDS即DQS,而是CK和CK#。而没有Initial Latency的就更简单了,直接数据就跟在CA后面,下面贴出官方Specification的是时序图。

有道云笔记

2021-11-08 11:34:45

评论 (0)